对汽车片上系统采用双核架构

例如,ALU内的错误会造成计算结果不准确,但是只要这些结果只影响内核寄存器值,那么它们就不会对系统运行产生危害。但是,如果这些寄存器被用于某些外部应用,那么就会引起故障。同样,在SoR内部传递的错误不会产生直接的危害,比如,如果错误的寄存器值被写入INTC,那么不会对系统的整体行为产生影响。同样,如果这个被错误写入的INTC寄存器触发了一次故障中断,那么系统也会发生故障。

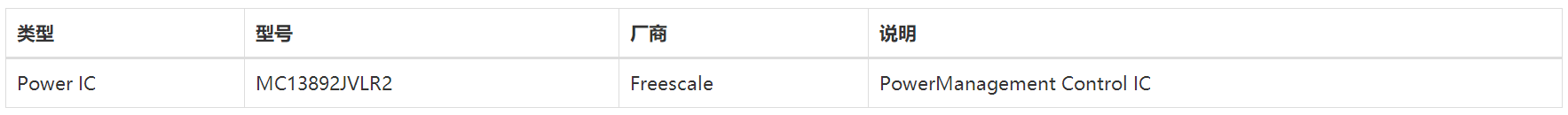

本文引用地址:http://www.amcfsurvey.com/article/116945.htm冗余校验器单元将检查由于外部总线数据在两个处理单元之间不一致而引起的故障。校验器单元将检测这些故障,然后将其传递到另一个名为故障收集和控制(FCCU)的模块。FCCU随后根据检测到的故障的性质采取修复操作,并使SoC进入已定义的安全状态。

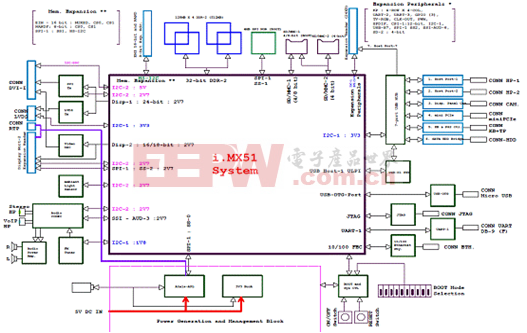

去耦并行模式:

在DPM中有两个独立运行的相同内核,与之形成对比的是拥有主处理器和协处理器的同构双核架构,其中协处理器的能力要比主内核更弱一些。这种配置为安全应用中的SoC提供了更高的性能。DPM在硬件层面上没有针对随机硬件故障提供内在保护。因此,对于安全应用中使用的DPM,必须在软件层面上引入一定程度的冗余。这可以通过多种方式实现,例如,采用主校验器方法,这种方式将运行独立的检查软件,检查另一个内核中的安全应用是否运行正常。

考虑到嵌入式系统/汽车领域中并不是所有应用都要求具备严格的安全性,因此还可以将MPC564xL配置为DPM以增强性能。

DPM相对于协处理器方式的架构优势:

DPM SoR有一个优点。它有两组外围设备,其中包括CPU内核、DMA控制器、中断控制器、交叉总线系统、内存保护单元、闪存控制器和RAM控制器、外设总线桥、系统定时器和看门狗定时器。这使它拥有比普通双核系统(处理器和协处理器)更高的性能。

Core0可以使用STM0、SWT0、MPU、MPU等控制应用和访问从外围设备。Core1与Core0类似。在复杂应用中,操作系统运行在SoC上,这些冗余配置的外设在控制每个内核上的应用时具有显著的优势。

DPM中的每个内核都包括一个RAM控制器和半个RAM阵列。当内核执行不同应用时,堆栈、临时结果等变量以及每个内核将使用的类似数据都将保存在各自的半个SRAM阵列中。这可以防止由共享引起的内存带宽瓶颈和故障。

两个内核都可以访问两个AMBA交叉开关,因此很有可能出现其中一个内核阻塞或明显拖延另一个内核通过交叉开关的情况。这个问题可以通过交叉客户端中的仲裁优先级解决。

评论