基于TLV1562的四通道高速实时数据采集系统的设计

下列条件:

VREFP=AVDD-1V ;

AGND+0.9VVREFM ;

3V>=(VREFP-VREFM)>=0.8V 。

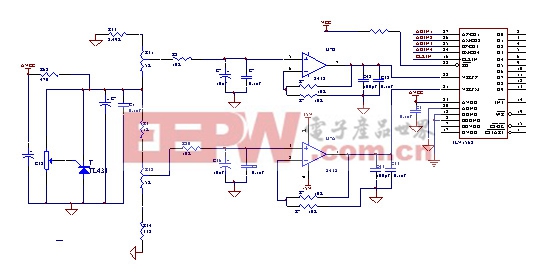

所以设计中采用图3所示的基准设计。通过调整R31和R32,使VREFP与VREFM满足上诉要求。

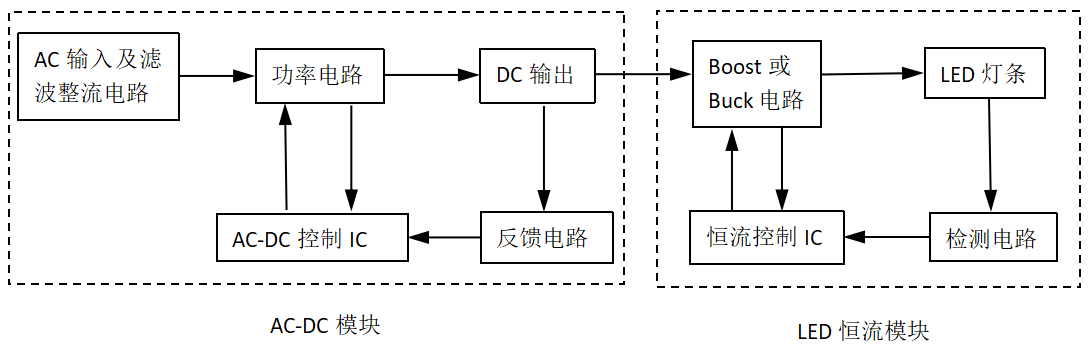

2.3 采集系统的设计

2.3.1 接口时序图

CPLD与TLV1562的接口时序图见图3。DISTANCE_PULSE是距离门脉冲,周期为512μs(80Km)或1024μs(160Km),SAMPLE_PULSE是采样开始脉冲,一旦监测到其上升沿采集系统就开始启动,START被置为高电平,TLV1562的CS置为低。WR、RD、INT的时序图是TLV1562的内部转换模式时序图。当WR出现两次低电平后,便完成了对寄存器CR0和CR1的配置,即实现了A/D转换的初始化。A/D转换结束,输出低电平信号INT有效,信号RD读取A/D转换结果并复位INT信号,完成一个转换周期,并开始准备下一次转换。

|

| 图3 EP1K100与TLV1562的接口时序图 |

评论