TS流的CRC译码器设计

3 UART设计

UART的程序采用了自顶向下的分模块设计方法,其功能模块主要分为波特率产生模块、起始位检测模块、发送模块和接收模块四部分。各个模块分别编写好并且仿真通过之后,再在顶层对其进行例化,使各个模块能够连接起来。

3.1 波特率产生模块

设计采用的波特率为9 600 b/s,帧格式为1 b起始位,8 b数据位,无奇偶校验位,1 b停止位。波特率的产生主要是使用累加的方法,当累加到一定值的时候,就给clk_bps一个时钟的高电平,从而产生波特率。产生波特率的部分代码如下:

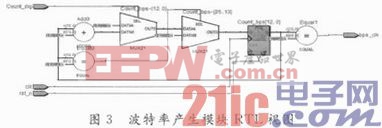

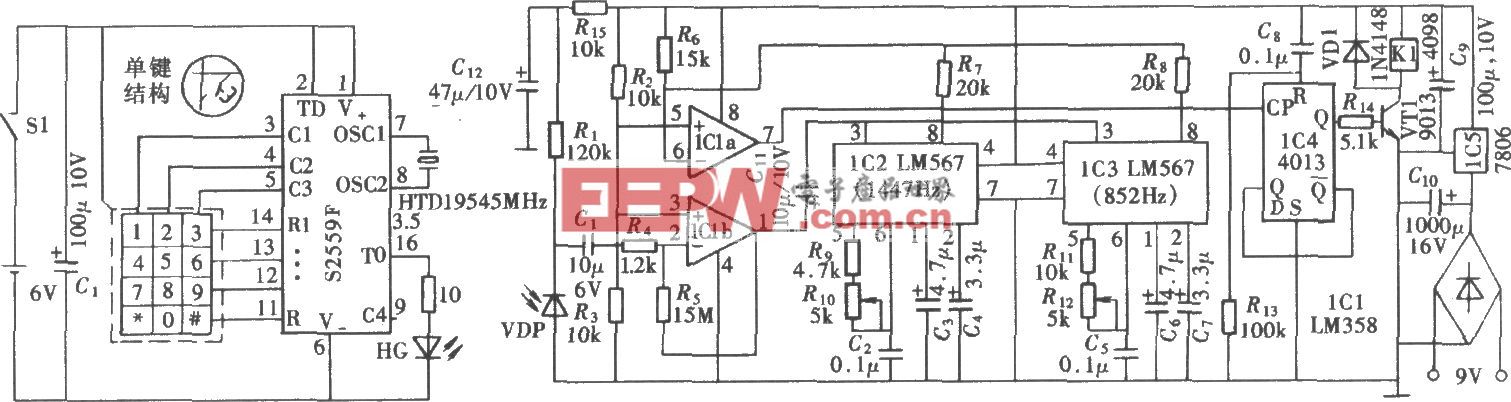

波特率产生的RTL视图如图3所示。本文引用地址:http://www.amcfsurvey.com/article/189722.htm

3.2 起始位检测模块

起始位是UART传输数据的开始,因此起始位检测的好坏至关重要,本设计采用了边沿检测技术来检测起始位,当起始位的那个下降沿到来的时候,H2L_sig端口就会产生一个时钟周期的高电平,为下面的接收做好准备,起始位检测的部分代码如下:

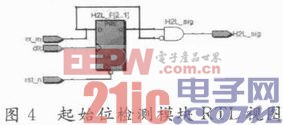

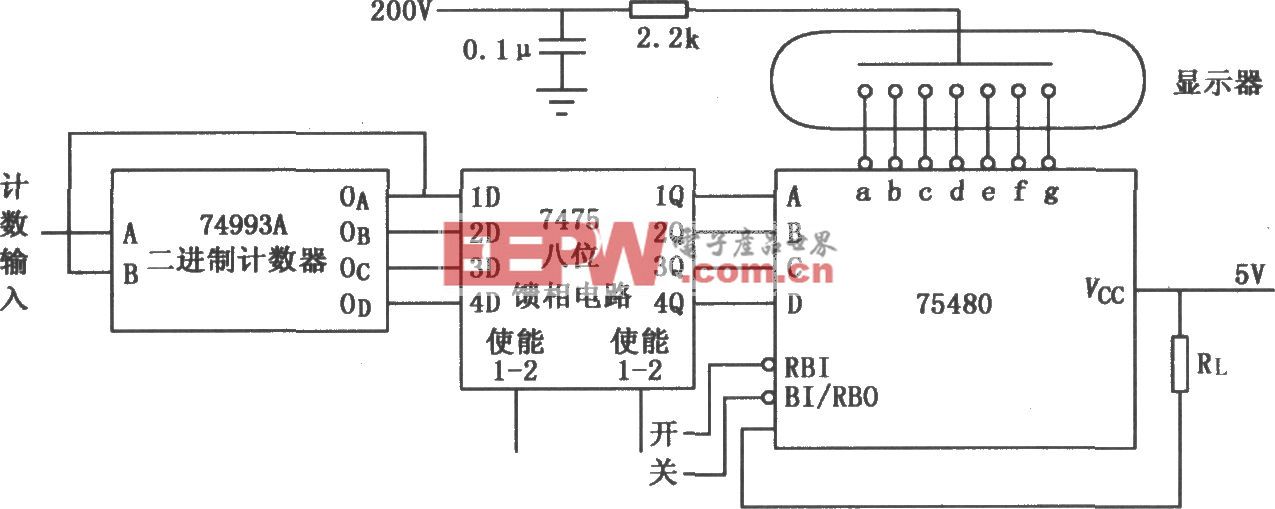

起始位的RTL视图如图4所示。

3.3 发送模块

发送模块主要功能就是将FIFO里8 b的数据按9 600 b/s波特率一位一位地发送出去,最后再加上停止位,其RTL视图如图5所示。

评论