基于DDS IP核及Nios II的可重构信号源设计

2.3 波形存储器ROM的设计

该模块完成相位/振幅转换电路的功能。在本设计中,要求DDS IP能输出正弦波、方波,三角波、锯齿波。可以用FPGA内部的LPM_ROM模块制作4张ROM表,分别存储4个波形的数据。实际上,由于方波和三角波是实现算法相对简单,为了节省资源,本系统直接用Verilog HDL描述其功能。实现产生方波信号的关键代码如下:

正弦波、锯齿波的产生是利用FPGA的LPM_ROM模块来实现。为了对ROM模块内的数据进行加载,首先应建立相应的*.mif(Memory Initial File)文件。它可以用C语言编写源程序,得到对应波形的数据,生成*.mif文件,如生成正弦波形数据的C语言程序如下:

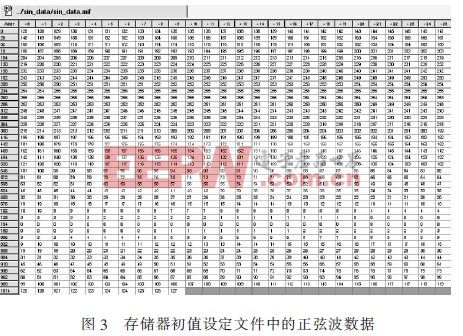

然后在Quartus II里新建.mif文件,把用命令字符生成的.mif文件的内容粘贴到Quartus II里新建的存储器初值设定(.mif)文件里面,如图3所示。再用Quartus II软件定制LPM_ROM,并加载刚才建立的.mif波形文件初始化ROM。

评论