基于FPGA的数字三相锁相环优化设计

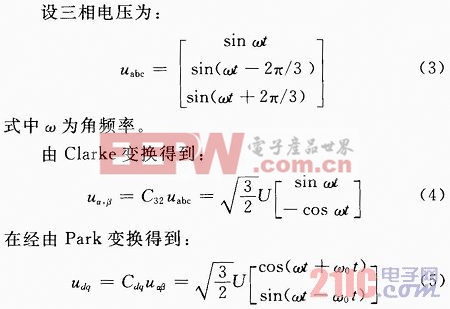

式中:U为电压的有效值。

锁相环

未锁定时q分量为一交流分量,与已设的分量q*=0比较得到一直流分量,以此完成鉴相。直流分量再经过由PI控制器组成的低通滤波器控制压控振荡器,最终使得ω与ω0相等,q分量为0,达到锁相。

未锁定时q分量为一交流分量,与已设的分量q*=0比较得到一直流分量,以此完成鉴相。直流分量再经过由PI控制器组成的低通滤波器控制压控振荡器,最终使得ω与ω0相等,q分量为0,达到锁相。2 三相锁相环

的系统仿真

的系统仿真根据图1三相锁相环

的拓扑结构,在Matlab/Simulink中搭建系统仿真模型。三相电压为220 V,采样频率为fs=5 kHz,压控振荡器的中心频率为f=50 Hz,通过仿真调整,最终确定Kp=0.02,K1=0.001,使锁相环

的拓扑结构,在Matlab/Simulink中搭建系统仿真模型。三相电压为220 V,采样频率为fs=5 kHz,压控振荡器的中心频率为f=50 Hz,通过仿真调整,最终确定Kp=0.02,K1=0.001,使锁相环 锁相的速度与精度达到最佳效果。图2(a)是三相锁相环

锁相的速度与精度达到最佳效果。图2(a)是三相锁相环 在0.05 s内的三相电压ua,ub,uc仿真波形;图2(b)是三相锁相环在0.05 s内的两相旋转坐标下ud,uq仿真波形,d轴分量大约在0.01 s稳定为0,即0.5个周期达到锁相;图2(c)是三相锁相环在0.05 s内的三相电压a相位角θ与VCO输出相位角θ*的仿真波形,θ与θ*在0.01 s基本完全重合,达到锁相。结果表明,三相锁相环可在0.5个周期内快速、准确地锁定电网电压。本文引用地址:http://www.amcfsurvey.com/article/189839.htm

在0.05 s内的三相电压ua,ub,uc仿真波形;图2(b)是三相锁相环在0.05 s内的两相旋转坐标下ud,uq仿真波形,d轴分量大约在0.01 s稳定为0,即0.5个周期达到锁相;图2(c)是三相锁相环在0.05 s内的三相电压a相位角θ与VCO输出相位角θ*的仿真波形,θ与θ*在0.01 s基本完全重合,达到锁相。结果表明,三相锁相环可在0.5个周期内快速、准确地锁定电网电压。本文引用地址:http://www.amcfsurvey.com/article/189839.htm

fpga相关文章:fpga是什么

锁相环相关文章:锁相环原理

评论