Leon3软核的FPGA SelectMap接口配置设计

2.2 SelectMap接口配置硬件设计实现

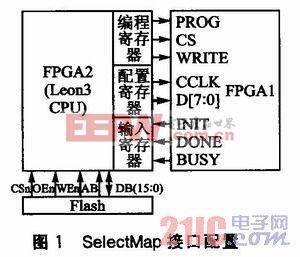

本文设计的SelectMap接口配置系统由两片FPGA和存储器(Flash)构成,如图1所示。设计中FPGA1选用了Xilinx公司Virtex系列芯片Vir-tex-5 XC5VSX95T,是需要进行配置的芯片。FPGA2内部嵌入了Leon3 CPU软核,可利用该CPU软核的存储控制器模块对Flash进行读写控制;利用FPGA内部丰富的资源,在FPGA2内部集成一个自定义的SelectMap接口控制IP核,主要用来产生FPGA的配置信号,这些SelectMap配置信号的状态由嵌入在FPGA2内部的CPU Leon3软核监控。该设计采用开源的Leon3软核CPU,并且充分利用了FPGA丰富的资源,与通常的SelectMap配置系统相比,设计成本低,设计较灵活。本文引用地址:http://www.amcfsurvey.com/article/191145.htm

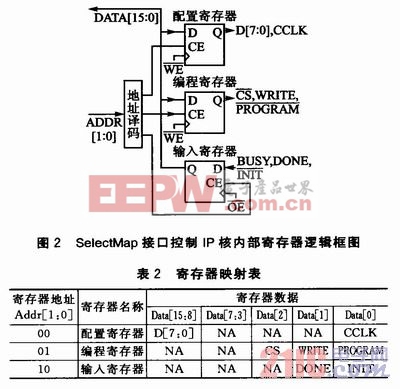

Flash存储器采用Intel公司的JS28F256P30T95,具有32 MB的存储空间,用来存储FPGA1的配置数据。因为Flash的每个地址空间中存储着16位数据,Leon3 CPU处理器读取Flash地址中的数据,然后把数据以字节形式传送到FPGA2。这个过程中,CPU处理器所在的FPGA2为FPGA1提供配置时序控制信号。这些控制信号的产生由FPGA2内部集成的SelectMap接口控制IP核实现。该IP核的功能模块由3个寄存器组成:配置寄存器、编程寄存器和输入寄存器。每次CPU对Flash进行读或写操作时,这些寄存器存储FPGA1的配置信号数据。其中配置寄存器和编程寄存器为只写寄存器,输入寄存器为只读寄存器。详细的逻辑框图如图2所示。CPU数据线在SelectMap接口控制IP核内部寄存器的构成如表2所列。

评论