基于FPGA的CAN总线控制器设计

2 系统验证

整个系统的功能仿真和时序仿真是借助Modelsim软件完成的。图4所示是对控制器发送数据的验证,测试用的发送数据为随意选择的:00101001,仲裁场和控制场也是任选的,分别为:110100101110、110001,设置好寄存器组后,控制器计算出对应的CRC码为:110111001111 011,之后控制器将数据按CAN协议的帧格式打包逐位发送出去。本文引用地址:http://www.amcfsurvey.com/article/191153.htm

控制器最初处于总线脱离模式,复位结束后进入总线启动模式,当控制器检测到总线上的1次连续11个隐性位时,进入总线空闲模式,接着当控制器检测到总线出现第一个显性位时,进入模式选择模式,在此模式下,控制器进行的操作就是总线仲裁,确定本节点是否获得总线控制权,由于本测试采用的是控制器自测模式,即输出线与输入线连在一起,所以仲裁时间为12个位时间,仲裁成功后,控制器会进入发送模式,若无错误产生,数据发送完成后控制器进入间歇模式,最后进入总线空闲模式。

经过一系列的测试验证后,表明本CAN总线控制器能够发送或接收所有符合CAN2.0A协议的报文帧。

3 结束语

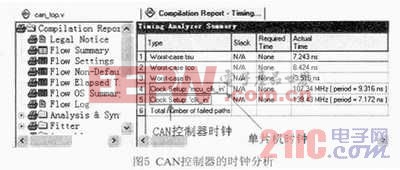

本设计实现了所有符合CAN2.0A协议的CAN总线控制器功能,最高工作频率为139.43MHz,这也达到了最初的设计目的。控制器的时序分析如图5所示。

本文作者创新点为:首先控制器的外围接口采用Avalon总线接口,这使得本设计的通用性更强:其次是本设计的最高工作频率达到了139.43MHz,能够适应高速通信的要求。

评论