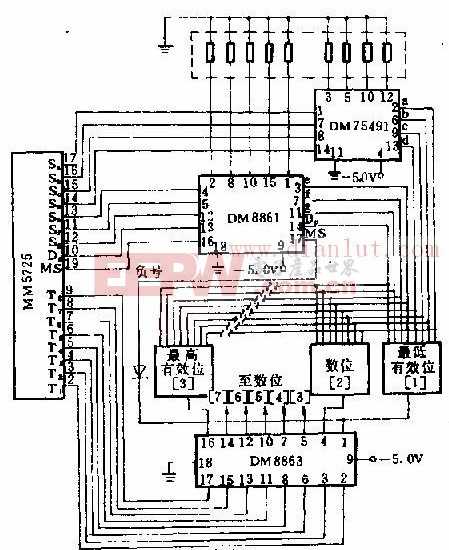

基于FPGA 与VHDL 的微型打印机的驱动设计

2. 2 软件设计

软件平台采用A ltera 公司的FPGA 开发平台Q uartus 。

Quartus 提供了一种与器件结构无关的设计环境,设计者不需要精通器件的内部结构,只需要运用自己熟悉的输入工具( 如原理图输入或数字电路描述语言输入) 进行设计,利用Quar tus 可以将这些设计转换为最终结构所需要的格式。有关结构的详细知识已写入开发工具软件,设计人员无需手工优化自己的设计。软件的开发流程如图4 所示。

图4 软件开发流程图

使用VHDL 硬件描述语言来进行软件设计。

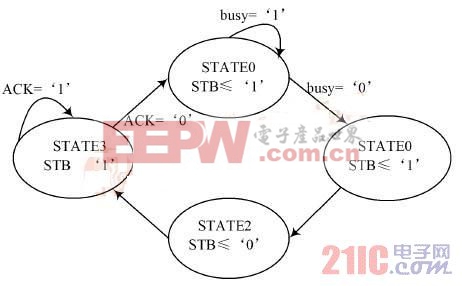

对微型打印机的驱动主要是对其工作时序进行正确的控制,利用VHDL 常见的状态机来实现对打印机的工作时序的控制,根据时序图1 所示的时序,状态机使用4 个状态,状态转换图如图5 所示。

初始状态STA TE0 时,数据选通触发脉冲信号STB 置“1” ( 高电平) ,检测打印机是否正忙,如果打印机为空闲状态( busy= “0”) ,转入下一状态STAT E1,否则( busy = “1 ” ) 继续执行ST AT E0; 在状态STAT E1,将数据写入打印机,直接转入下一状态; 在状态STAT E2,将数据选通触发脉冲信号STB 置“0” ,打印机读数据,转入下一状态; 在状态ST ATE3,检测数据是否已经被接受,若数据已被接受( ACK = “0” ) ,打印机转入初始状态ST AT E0,等待接受新数据,若数据未被接受( ACK = “1” ) ,继续执行STAT E3 直到数据被接受。

图5 状态转换图

3 结 语

使用FPGA 与V HDL 硬件描述语言设计的微型打印机驱动,通过系统调试能够完成对打印机的时序控制,目前已经在某型测试仪中正常使用。该设计系统控制简单,抗干扰性强,可靠性高,移植性较好,能够用于任何使用FPGA 芯片的系统中,具有一定的应用前景。

评论