基于FPGA 的卫星便携站的同步数字复接器的设计

1.2 设计方案

1.2.1 帧结构

该单元不要求与其他复分接设备互联互通,所以采用自定义的帧结构。帧头采用集中帧码,帧头固定为12 bits。帧结构如表1 所示。

根据表1 可以计算出每帧的帧长L 为7 680 bit,线路速率R 为768 kbps 时,帧周期T 为:

帧频F s 为:

表1 帧结构

1. 2. 2 复接器

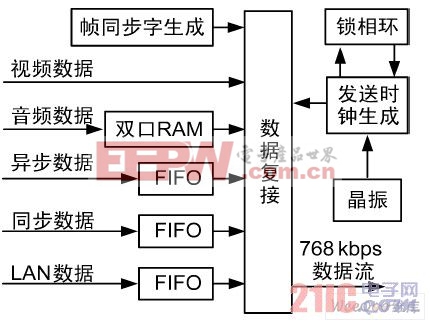

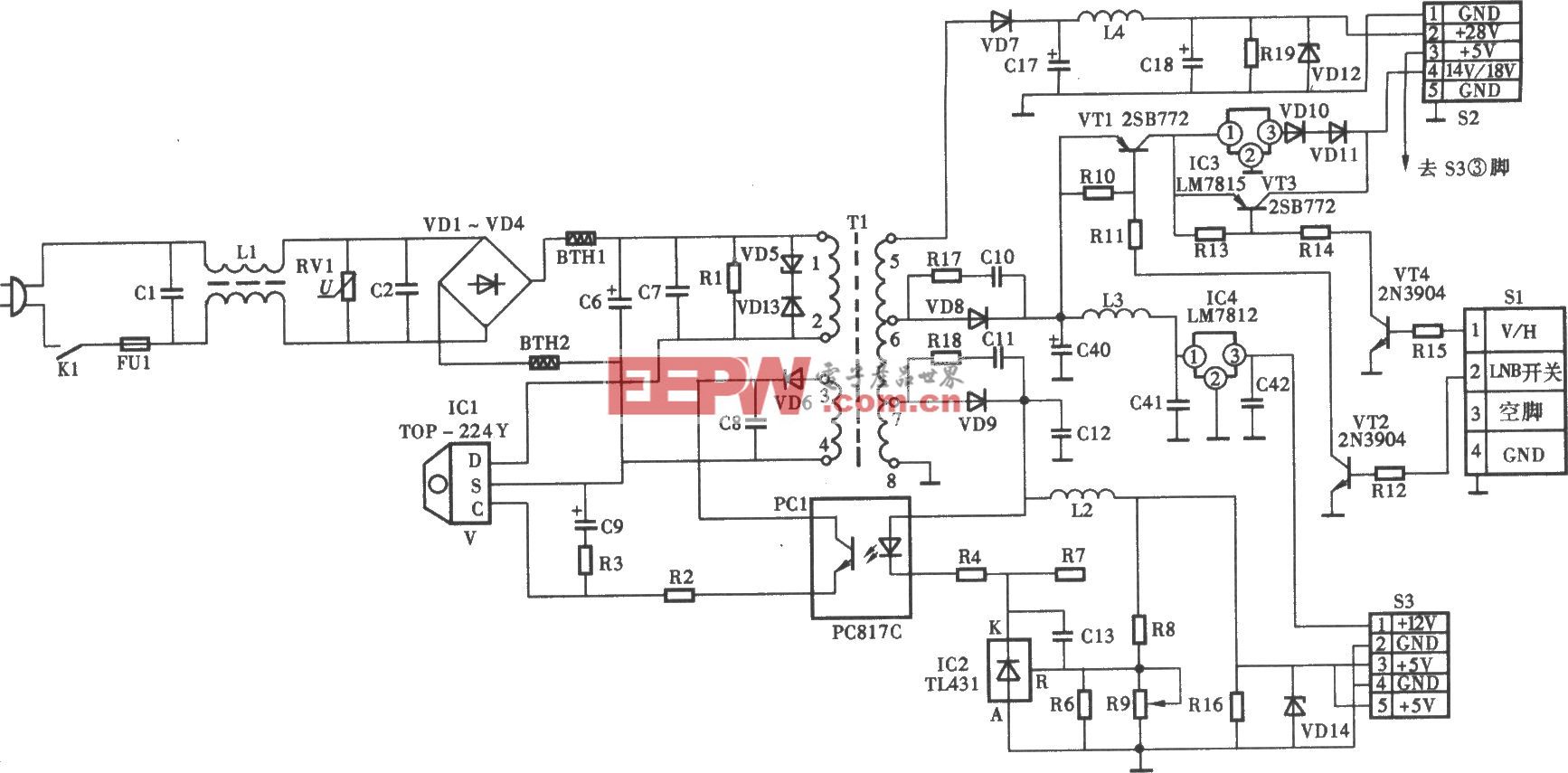

复接器部分负责将各支路信息数据和帧头合成一路数据流。它由时钟发送电路、数据接收存贮器、数据缓冲单元和数据复接电路组成。时钟发送电路产生复接各支路信息数据所需的时隙,时钟通过使用内部时钟源或由接收时钟锁相得到; 数据接收存贮器为一双口RAM,用来接收数字音频数据; 数据缓冲单元用来把同步数据等数据的相位调整到满足可以进行复接的相位; 数据复接电路将上述数据合成一路线路数据; 复接器的组成框图如图2 所示。

图2 复接器组成框图

评论