基于FPGA的高速宽带跳频发射机的中频设计

本系统基带调制采用最小频移键控,即MSK调制,输入码元速率为5Mbps。由于FPGA处理能力较强,可以选择相对较高的数据速率,这样可以降低数字上变频的复杂度。但同时会增加基带成形滤波器设计的复杂度,需要折中考虑。本系统选择基带数据速率为25M/B。

成形滤波器采用最优化设计中的等波纹法设计,设计指标如下:采样率25MHZ,通带截止频率为3.75MHZ,阻带截止频率5MHZ。通带波纹0.2dB,阻带衰减80dB。利用FDATool工具进行滤波器的设计,系数量化为定点16bit,阻带衰减可以达到75dB以上。

2.3 数字上变频

2.3.1 内插

完成基带调制和成形滤波后,FPGA内部数据速率为25MSPS,然后需要进行数字上变频,最终使数据速率达到AD9736的数据转换速率,即800MSPS。由25MSPS到800MSPS需要进行32倍内插,如果用一次内插实现,需要插值滤波器具有很高的阶数,其计算量和存储空间都比较大。在这种情况下,一般采用多级内插,多级实现的主要优点是:

(1). 大大减少了计算量;

(2). 减少了系统内的存储量;

(3). 简化了滤波器的设计;

(4). 降低了实现滤波器时的有限字长的影响,即降低了舍入噪声和系数灵敏度。

多级内插的缺点是增加了控制程序的复杂程度,所以并不是分级越多越好所以在设计时应该折中考虑。一般来说,3至4级插值对于降低运算量和存储量的帮助很明显,级数再多时,效果就不明显了。这里我们将插值分为4级,分别为2倍,2倍,2倍,4倍。抗镜像低通滤波器都采用等波纹设计,考虑到滤波器性能和资源占用的折中,需要利用MATLAB仿真确定各级滤波器的阶数和系数位宽。

经过三级2倍内插后,FPGA内部数据速率达到200MSPS,基本已经达到了Cyclone III内部处理能力的极限,最后一级利用多相结构,完成串并转换,输入200MSPS数据速率,4倍内插后,输出四路,各路均为200MSPS数据速率。下面以4倍内插,8阶低通滤波器来说明多相滤波器的原理。

由于在内插的过程中插入的0值与系数相乘是没有意义的,所以对于4倍内插,8阶低通滤波器来说每次滤波只需要2次乘法。这样就将乘法的运算量降低为原来的1/4。滤波器每次输入一个新的数据,就用4个子滤波器分别计算一次,然后以4倍的输入速率顺序输出。所以可以用4个子滤波器组成的滤波器组实现多相插值滤波。

2.3.2 并行数控振荡器

完成插值后,数据速率达到并行4路,每路各200MSPS。然后进行载波调制。最后,利用LVDS模块进行并串转换,实现800MSPS MSK调制输出。

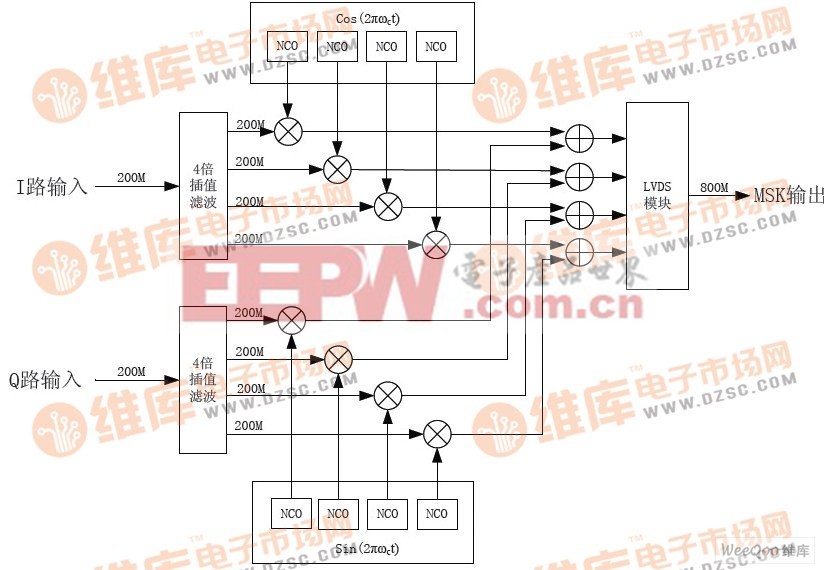

由于FPGA内部处理能力的限制,用于载波调制的NCO也需要设计为并行结构。载波调制的实现框图如图3所示:

图 3 4路并行载波调制结构图

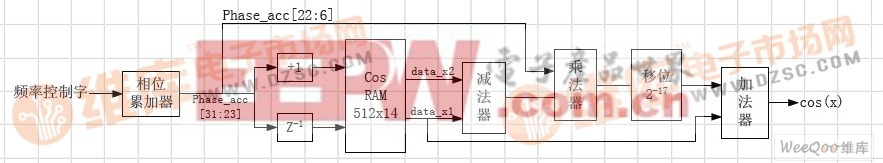

为了保证NCO输出波形具有较高的杂散抑制比,同时要占用较少的资源,一般采用插值法。插值法结合了查表法和计算法的优点,在保证频谱具有较高杂散抑制比的同时占用较少的资源。

插值法是指利用相位累加器的高位进行查表,用相位累加器的低位进行插值运算,这样使用相位累加器的有效位数较差,保证相位舍位噪声较小,同时也降低了存储器的大小。

最简单且有效的插值法为一次线性插值,计算公式如下:

其中要插值的数据y位于 之间,

之间,  为斜率,

为斜率, 到y的水平距离。FPGA实现一次线性插值需要一次乘法,两次加法,以及一次移位运算。避免了占用过多的存储器资源。

到y的水平距离。FPGA实现一次线性插值需要一次乘法,两次加法,以及一次移位运算。避免了占用过多的存储器资源。

图4是插值法NCO的实现框图:

图 4 插值NCO实现结构图

本设计要求NCO输出数据速率为800MSPS,采用4路并行设计,每一路输出数据速率均为200MSPS。这样需要4个NCO模块。每个子NCO模块的频率控制字是对于整体800MSPS数据速率NCO频率控制字的4倍。且每个子NCO的初始相位相差一个整体NCOd的频率控制字。例如,要产生200M的正弦和余弦信号。计算得整体NCO的频率控制字为:

4路子NCO的频率控制字均为: 。4路子NCO初始相位相差

。4路子NCO初始相位相差 。

。

评论