基于FPGA的微型数字存储系统设计

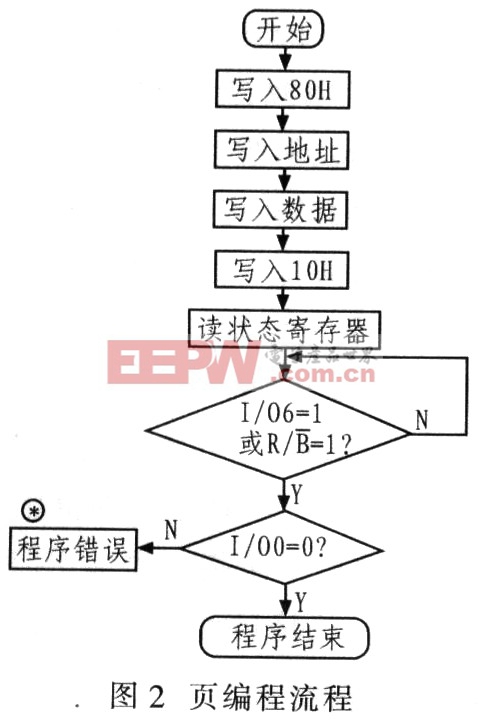

读操作较为复杂,需要XC2S50和CY7C68013协同工作。这里只给出读信号的操作过程。先写人读设置命令00H,因为读一次执行一页,所以地址的写入是2个行地址和3个列地址,之后写入读命令,在等待rb变高后就可发送re信号将数据从Flash读出。写操作过程与读操作类似,但写操作完全由 XC2S50控制,写完命令、地址后,开始写入数据,直到写满2 KB数据,最后输入页编程命令。需要注意每写完2 KB数据,Flash返回的状态信号rb所等待的时间较长,大约是140μs。图2为页编程的流程。本文引用地址:http://www.amcfsurvey.com/article/191913.htm

3.2 CY7C68013控制逻辑及固件程序设计

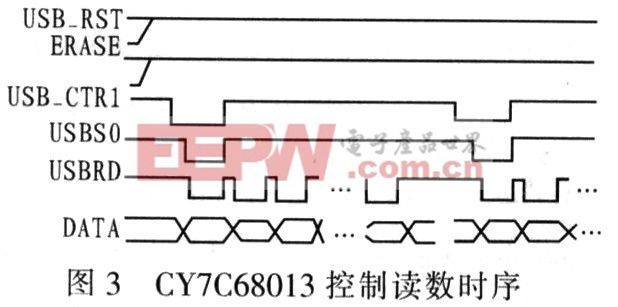

CY7C68013主要完成两部分工作,一是实现对擦除的控制开关命令,即上位机通过USB接口发送擦除命令,CY7C68013接收到这个命令后,会发送一个约为200 ms低脉冲通知FPGA启动擦除操作;二是通过与FPGA配合,完成从Flash通过CY7C68013的GPIF接口读入上位机的任务。 CY7C68013所用到的I/O包括控制线USBCTR1,状态线US-BS0,读信号线USBRD及8条数据线。

读数时,首先由单片机发出读数开始命令USBCTR1,FPGA接收到该命令后开始初始化,包括写入读数设置命令、地址及读数命令,等待rb变高, USBS0置低,当单片机检测到USBS0变低后,开始给出一系列脉冲GPIF(USBRD),将2 KB数据依次读出。与此同时,FPGA在等待几百纳秒后将USBS0置高,单片机在判断USBS0变高后也将USBCTR1拉高,为下一页读数做准备。读数时序如图3所示。

按照上述控制逻辑关系编写CY7C68013的同件程序。CY7C68013有3种可用接口模式:端口、GPIF主控和从FI-FO。“GPIF主控”接口模式使用PORTB和PORTD构成通向4个FX2端点FIFO(EP2、EP4、EP6和EP8)的16位数据接口。GPIF作为内部的主控制器与 FIFO直接相连.具有6个可编程控制输出信号(CTR0~CTR5)和6个通用准备就绪输入信号(RDY0~RDY5),用户可通过编程设置控制信号的输出状态,即器件在接收到何种就绪信号后执行相应操作,GPIF控制代码存放于器件内部RAM的波形描述器中。从该系统需求出发,将CY7C68013设为FIFO Read模式,使GPIF中的Slave FIFO与USB通信中端点缓冲直接建立连接,数据传送无需CPU参与。

评论