基于Verilog的FPGA与USB 2.0高速接口设计

IDLE:当写事件发生时,转到状态1。

状态1:指向IN FIFO,激活FIFOADR[1:O],转向状态2。

状态2:如果FIFO满标志为“假”(FIFO不满),则转向状态3;否则停留在状态2。

状态3:传送总线驱动数据。为一个IFCLK激活SLWR,转向状态4。

状态4:如果有更多的数据要写,则转向状态2;否则转向IDLE。

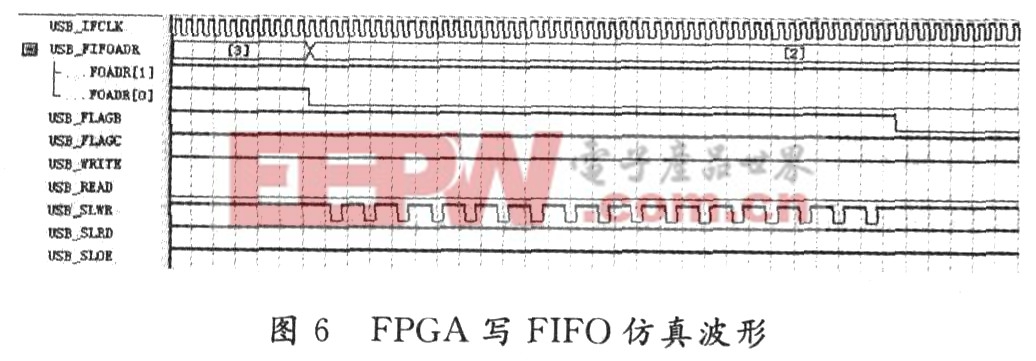

用QuartusⅡ进行仿真验证,其仿真波形如图6所示,在此过程中USB_SLWR信号很重要,经分析可知,本状态机实现的FIFO写控制信号完全正确。

3 实验结果

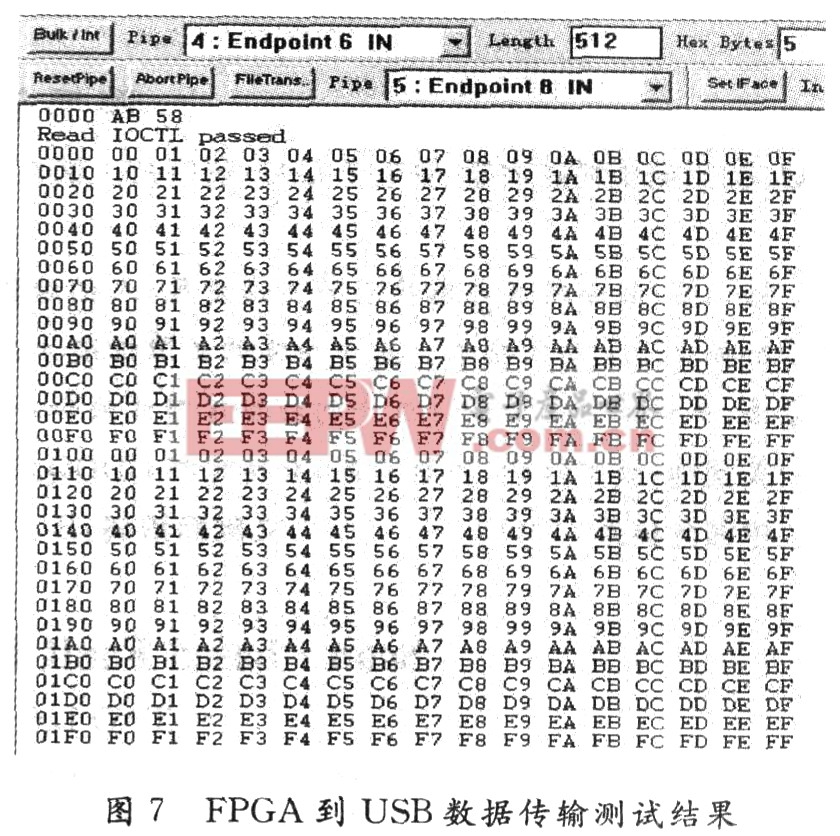

对传输的数据进行验证,可通过FPGA编程生成O~255的数据传送至CY7C68013的EP6端点,连续传送两次,然后利用EZ一USB Control Panel软件测试所接收到的数据,测试结果如图7所示,可以看出,数据传输准确无误。

4 结 语

USB 2.0控制器CY7C68013已经被广泛应用到许多数据传输领域,由于USB具有灵活的接口和可编程特性,大大简化了外部硬件的设计,提高了系统可靠性。该设计可扩展性好,已经被应用于数据传输与采集的板卡上,经实际测试,没有出现数据的误码等错误,数据传送正确,传输速率可达30 MHz/s以上,满足设计要求。

评论