IPU:为AI处理器带来了一种颠覆 性架构

迎 九 (《电子产品世界》 北京,100036)

本文引用地址:http://www.amcfsurvey.com/article/202007/415317.htm摘 要:英国半导体之父、Arm的联合创始人Hermann爵士称:“在计算机历史上发生过3次革命,第1次是70年代的CPU,第2次是90年代的GPU,而Graphcore公司带来了第3次革命。”Graphcore推出了为AI计算而生的IPU。Graphcore高级副总裁兼中国区总经理卢涛先生和中国销售总监朱江,向电子产品世界等媒体介绍了IPU的架构。

0 引言

Graphcore总部在英国,目前全球有450名员工。公司已获大量投资,截止到2020年6月,总融资超过4.5亿美元。

Graphcore主要产品是IPU。Graphcore认为,由于CPU和GPU不是为了满足机器学习的计算需求而设计,因此尽管进化,创新者却开始因硬件阻碍而倒退。而Graphcore创建了一种全新的处理器,是第一个专为机器学习工作负载而设计的处理器——智能处理器(IPU)。

1 IPU的两大特点

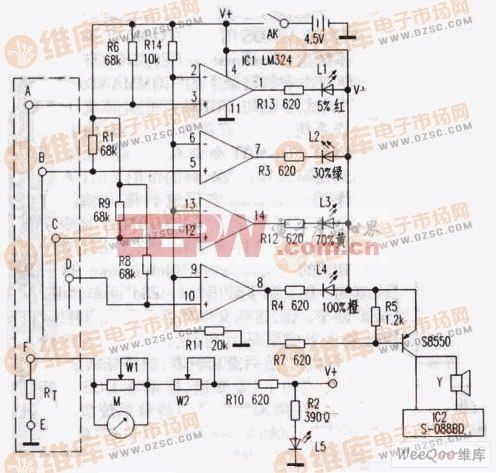

Graphcore现有的IPU的表现及下一代的模型上,性能领先于GPU:在自然语言处理方面的速度能够提升20%~50%;在图像分类方面,能够有6倍的吞吐量而且是更低的时延;在一些金融模型方面的训练速度能够提高26倍以上。目前,IPU在一些云上、客户自建的数据中心服务器上已经可用。

相比GPU及其他与GPU类似的处理器架构,IPU有2个亮点设计。

1)从大规模并行的角度来看,CPU在控制方面做了很多非常通用化的处理器,也就是一个标量的处理器;GPU是向量处理器,有单指令、多数据的特点,适合处理大规模的、稠密的数据,在某一类的AI运算里会有非常明显的优势,这也是现在GPU在市场上表现得非常好的原因;而IPU是一种全新的架构设计,是一种图形的处理器,具备多指令、多数据的特点。除了稠密的数据之外,现在代表整个AI发展方向的大规模稀疏化的数据,在IPU上处理就会有非常明显的优势。

2)IPU采用的大规模分布式的片上SRAM的架构,这与GPU、CPU是完全不同的。Graphcore IPU抛弃了外部的DDR,把所有memory放到片上,因此能够解决在目前机器学习中大量出现的内存带宽构成的瓶颈。

在场景应用方面,由于采用了分组卷积这种新型的卷积,和目前比较传统的ResNet相比,可以有更好的精度表现。但这样的分组卷积因为数据不够稠密,在GPU上可能效果并不好,而IPU可以把这样的模型真正落地使用,尤其是在一些垂直行业,诸如金融领域提升应用的性能。

Graphcore所做的产品包括了硬件、软件和IPU的系统解决方案。

2 为AI应用打造的IPU

机器智能代表的是全新的计算负载,特点是非常大规模的并行计算,和非常稀疏的数据结构。AI或机器智能相较于传统的科学计算或者高性能计算(HPC)有个特点,就是低精度计算;另外像在做训练推理过程中的数据参数复用、静态图结构都是AI应用代表的一些全新的计算负载。

从2016年至今,整个AI算法模型发展基本上从2016年1月的ResNet50的2 500万个参数,到2018年10月BERT-Large的3.3亿个参数,2019年GPT2的15.5亿个参数,呈大幅增长的趋势。甚至现在有一些领先的科研机构和AI研究者在探索更大的算法模型,希望用一些复杂的模型能够训练更复杂的算法,并提高精度。

但是现在的密集计算并不是可持续的,因为譬如要从15.5亿规模扩展到1万亿,计算方面的提高是指数级,即数倍算力的提升,这就需要一种全新的方法来做AI计算。

但是在当前,机器学习采用的还是传统处理器架构,例如CPU,目前还是有很多AI负载架构在CPU之上。CPU实际是针对应用和网络进行设计的处理器,是标量处理器(表1)。

后来出现的GPU是针对图形和高性能计算,以向量处理为核心的处理器,从2016年到现在被广泛应用在AI里。

但AI是一种全新的应用架构,它底层表征是以计算图作为表征的,所以可能需要一种全新的处理器架构,而Graphcore IPU就是针对计算图的处理来设计的处理器。

提到摩尔定律和算力,处理器现在是1个teraflops(每秒1万亿次浮点运算)、10个teraflops甚至100个teraflops,算力提升非常快。但人们发现,有效的算力其实远远达不到算力的峰值,中间内存的带宽是非常限制性能的。

例如,处理器算力提高了10倍,内存怎样提高10倍吞吐量呢?如果用传统的DDR4、DDR5、HBM、HBM1、HBM2、HBM3内存等,基本上每代只能有30%、40%的提升。

所以在Graphcore做IPU的时候,在这部分做了一个特别的设计:与传统的CPU、GPU比较起来,IPU用了大规模并行MIMD的处理器核,另外做了非常大的分布式的片上的SRAM,在片内能做到300 MB的SRAM,相对CPU的DDR2的子系统,或相对于GPU的GDDR、HBM,IPU能够做到10~320倍的性能提升。从时延的角度来看,与访问外存相比较,时延只有1%,可以忽略不计。

再从整体上看一下IPU处理器,目前已经量产的是GC2处理器,是16 nm TSMC的工艺。该处理器目前片内有1 216个IPU-Tiles,每个Tile里有独立的IPU核作为计算及In-Processor-Memory(处理器之内的内存)。所以整个GC2共有7 296个线程,能够支持7 296个程序做并行计算。对整片来说,In-Processor-Memory总共是300 MB。所以IPU的整个思想是所有的模型要被放在片内处理。PCIe也是16个PCIeGen 4。

所以,IPU GC2是非常复杂的拥有236亿个晶体管的芯片处理器,在120 W的功耗下有125 TFlops的混合精度、1 216个独立的处理器核心(Tile)、300 M的SRAM能够把完整的模型放在片内,另外内存的带宽有45 TB/s、片上的交换是8 TB/s,片间的IPU-Links是2.5 Tbps。

由于IPU GC2有1 216个核心(Tile)、7 000多个线程,所以解决并行硬件的高效编程问题是一个非常大的课题。Graphcore采用构建大规模数据中心集群的BSP技术(Bulk Synchronous Parallel,大容量同步并行),这种技术目前在谷歌、Facebook、百度这样的大规模数据中心都在使用。

因此,IPU是业界首款BSP处理器,通过硬件能支持BSP协议,并通过BSP协议把整个计算逻辑分成计算、同步、交换。对软件工程师或开发者,这就是非常易于编程的,因为这样就不用处理locks这个概念。对用户来说,也不用管其中是1 216个核心(Tile)还是7 000多个线程、任务具体在哪个核上执行,所以这是一个非常用户友好的创新。

(注:本文来源于科技期刊《电子产品世界》2020年第07期第59页,欢迎您写论文时引用,并注明出处。)

评论