利用高效的编程技术发挥多内核架构优势

在低端嵌入式领域,单内核解决方案仍然存在。通过采用速度更快或带宽更宽的处理器仍有可能提升系统的功能和性能曲线。在高端领域,多内核是必然的发展方向。这正是双精度浮点算法经常出现并在超级计算机中长盛不衰的原因。事实上,台式机和机架安装系统(比如Nvidia的产品)正在将这种处理能力普及化。

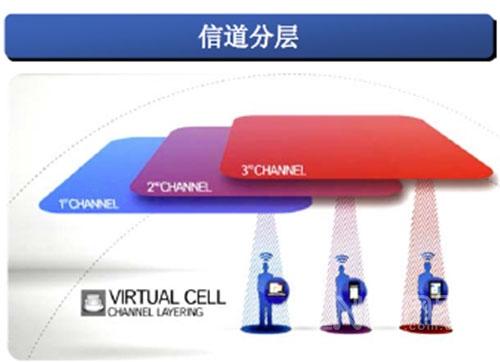

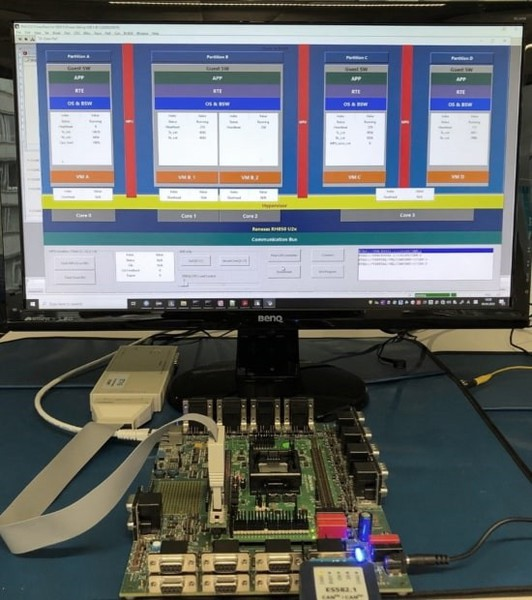

在讨论软件和多内核架构时经常提及的另一个问题是虚拟化。并不是所有多内核平台都支持虚拟化,但虚拟化确实能带来更好的机会。虽然虚拟化使得硬件设计面临更多的挑战,但它通常能简化软件和应用管理。

SMP服务器

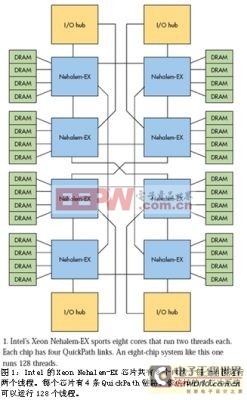

Xeon Nehalem-EX是Intel公司提供的顶级8内核对称多处理(SMP)平台。像8芯片、64内核系统这样的多芯片解决方案,通常采用高速QuickPath点到点互连技术将处理器和外设控制器链接在一起(图1)。使用过带HyperTransport链路的AMD Opteron处理器的工程师,对这种架构非常熟悉。在这两种情况下,最简单的配置是单个处理器通过单条高速链路链接到单个外设控制器。

除了提供分布式内存子系统外,Intel和AMD还实现了连贯缓冲非统一内存寻址(ccNUMA)技术。每个处理器芯片都有自己的内存控制器以及一级、二级和三级缓存。任何芯片都可以使用高速链路访问其它任何芯片中的内存。当然,离请求者越远的数据访问时间越长。这些高速链路也被用于消费设备,但只有到I/O中心的单条链路是必需的。换句话说,在共享内存访问时服务器将在处理器芯片间产生显著的流量。芯片至芯片流量和缓存管理是高效操作的关键。

HT Assist是AMD最新推出的Istanbul Opteron处理器的一个重要功能,它通过优化内存请求和响应过程来尽量减少相关事务处理的数量,进而释放出大量带宽用于处理其它业务(图2)。HT Assist实际上会跟踪数据在内核和缓存间的移动,允许请求得到具有所需数据的最近内核的服务。

最坏的情况是拥有片外存储器空间的芯片必须从片外存储器访问数据;最好的情况是发现数据正好位于运行着需要这个数据的线程的芯片缓存中;中间情况是内核从相邻芯片的缓存中获取数据。使用虚拟化和缓存技术后系统将变得更加复杂,并导致数据延时更加难以确定。这在确定性嵌入式应用中可能是个问题,但在大多数服务器应用中问题并不十分明显,因为这种情况下的速度比精细的确定性更加重要。

编程人员现在都在使用这些平台,因为它们能大大简化编程任务。同样,应用程序可以使用越来越多的内核,前提是应用程序可高效地利用充足的线程。高效使用多内核系统并不像表面看起来那么容易。缓存大小和应用程序工作数据集中的参考位置会影响特定算法的运行效果。

AMP应用处理器

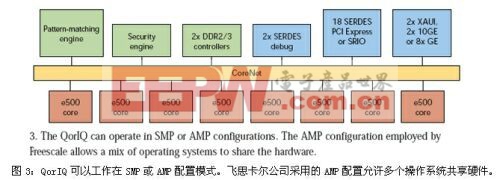

对称处理(SMP)架构对许多嵌入式应用来说非常有用,但非对称多处理(AMP)也有它的用武之地。AMP配置在很多地方都可以看到,从TI的OMAP(开放多媒体应用平台)到飞思卡尔的P4080 QorIQ都有AMP的身影(图3)。

评论