基于AVR和CPLD的高速数据采集系统的设计

输入系统的信息大多数是模拟量,为使计算机能够处理这些模拟量,必须经由数据采集系统将模拟量转化为数字量。CPLD是在PAL、GAL等逻辑器件的基础上发展起来的,CPLD的规模比较大,适合于时序、组合等逻辑电路的应用场合,它的高集成度能力大大缩小电路板的尺寸,降低了系统的成本,而且能够提高系统的性能和可靠性。对于一个成型的探测系统而言,通常都是有采集储存部分的,无论是电信号、光信号、声音信号、磁信号等在被探测器接收到后大部分都需要转化为数字信号传给处理器才能完成分析、判断的过程。对于需要高速采集并存储的系统,常常需要购买昂贵的高速采集卡等设备,在基于CPLD、AVR等控制高速ADC、储存等技术的基础上,本文设计低成本、高速采集存储的硬件实现。

1 系统总体设计方案

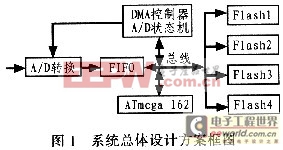

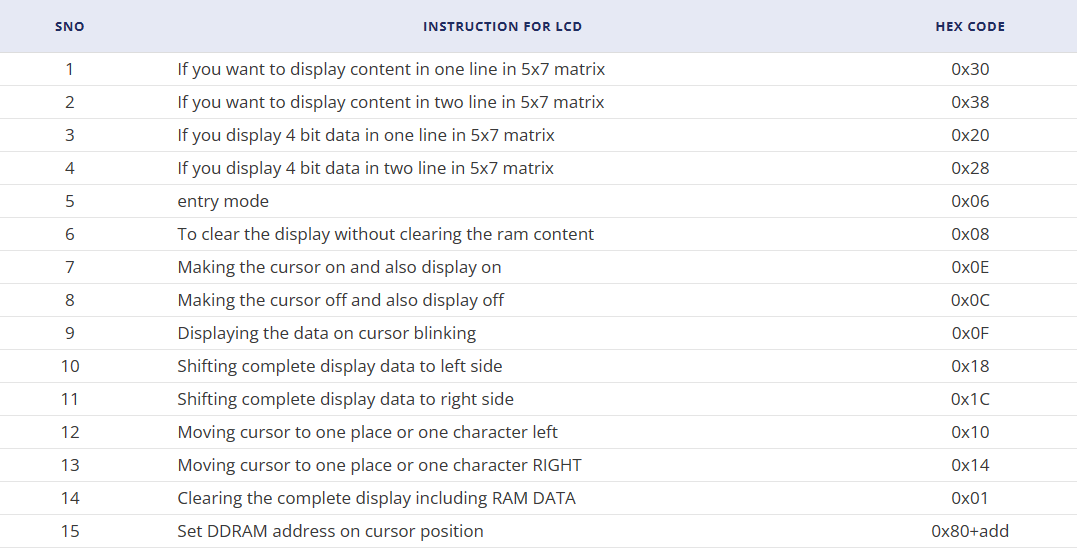

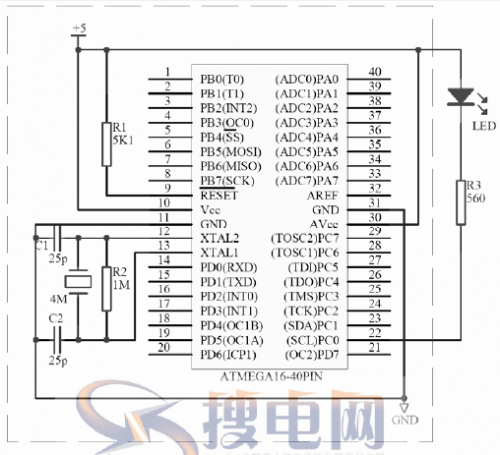

系统利用ATmegal62作为主控制器,CPLD用于产生控制时序,二者相结合协调进行数据的采集与传输控制。图1给出其系统总体设计方案框图。

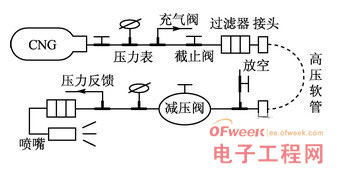

数据采集系统的工作原理是:模拟量信号经过传感器后转化成电压量,通过ADC将模拟量转换为数字量,而后进行传输存储和处理。在本系统中,在CPLD和AVR的控制下,将采集到的模拟信号经过A/D器件转换之后,转换结果先缓存到FIFO,再转存到非易失性Flash阵列中,其中FIFO不但可以实现缓存功能,还可以解决A/D转换之后数据位数跟Flash存储器的数据线位数不匹配的矛盾。

1.1 采集部分

本系统应用的A/D转换器是MAXl308,它具有8通道可编程配置,可接收数字输入分别激活每一路通道;100 ps通道间T/H匹配;转换时间为0.72(单通道),0.9(2通道),1.26(4通道),1.98μs(8通道);吞吐率为1 075(单通道),90(2通道),680(4通道),456千次/秒(8通道)。其他特性包括20 MHz T/H输入带宽、并具有内部时钟、内部(+2.5 V)或外部(+2.0~+3.O V)基准,以及低功耗省电模式。

1.2 控制与存储部分

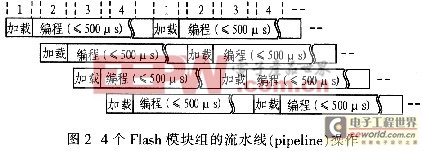

如图2所示是4个Flash模块组采用流水线(pipeline)操作,使用该方式可以克服Flash写入速度较慢的缺点。Flash存储器的写入有2个阶段:数据加载阶段(通过I/0端口将数据写入页寄存器)和编程阶段(在芯片内部,将页寄存器的数据传输到存储单元)。由于编程阶段是自动进行的,不需要外部系统的干预,控制器可以进行其他事务的处理,如有效块地址的运算等,从而节省系统开销。NAND型Flash存储器的写操作以流水线方式进行,首先加载第1个Flash模块组,数据加载完后,第1个模块组进入自动编程阶段:再加载第2个Flash模块组,数据加载完后,第2个模块组进入自动编程阶段;然后依次对第3个乃至第4个模块组进行操作,当第4个模块组数据加载完后,第1个存储模块组已经自动编程结束,接着再加载和自动编程形成流水线的工作方式。从整个系统总体效果来看,它一直在进行存储加载数据。

评论