基于多环锁相宽带细步进频率合成器的设计

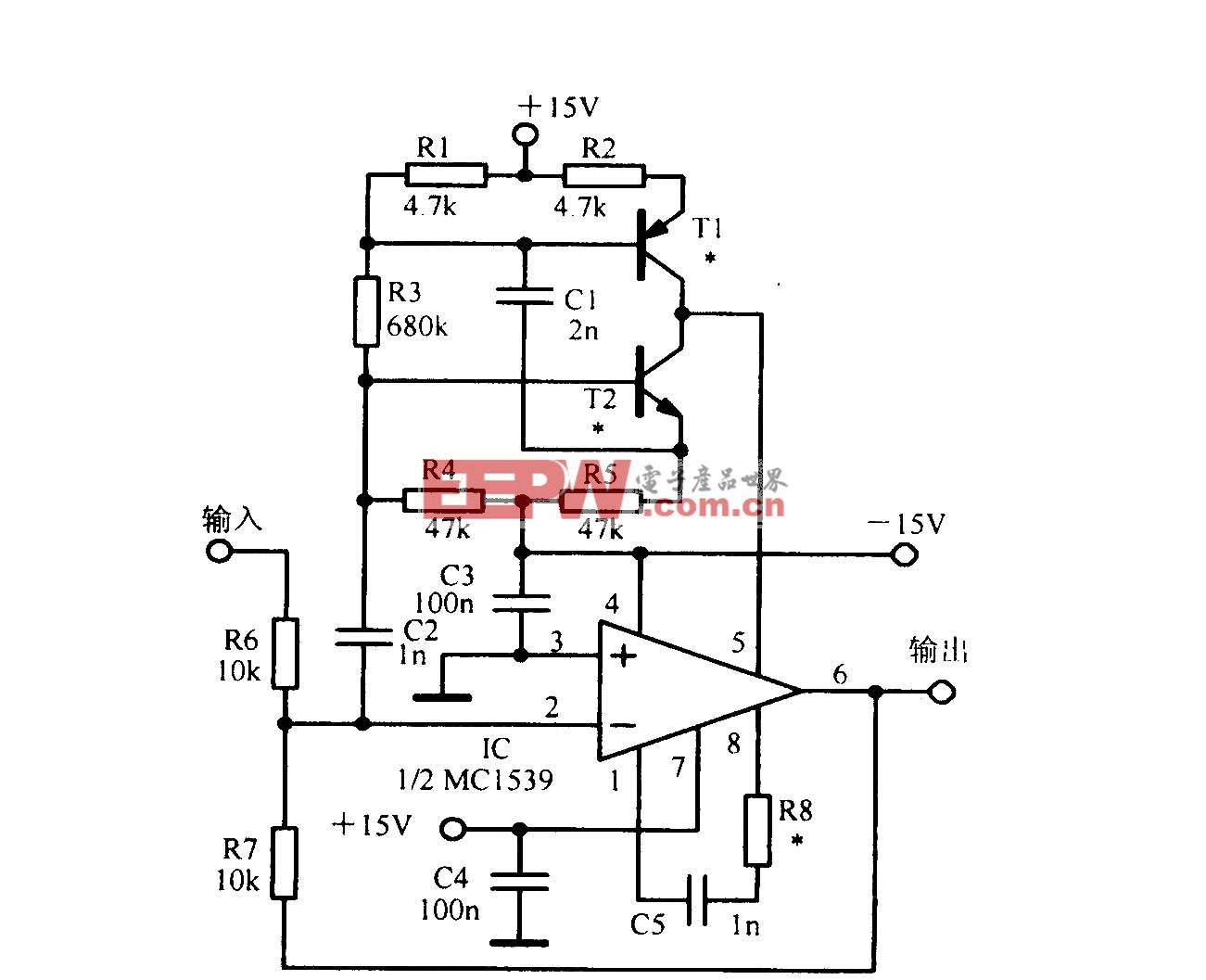

末级锁相环

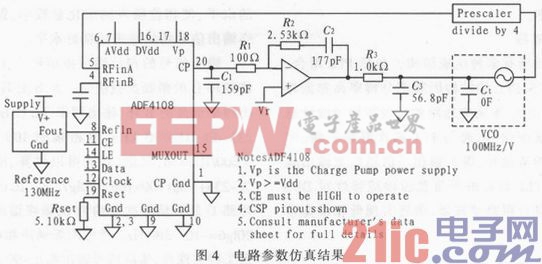

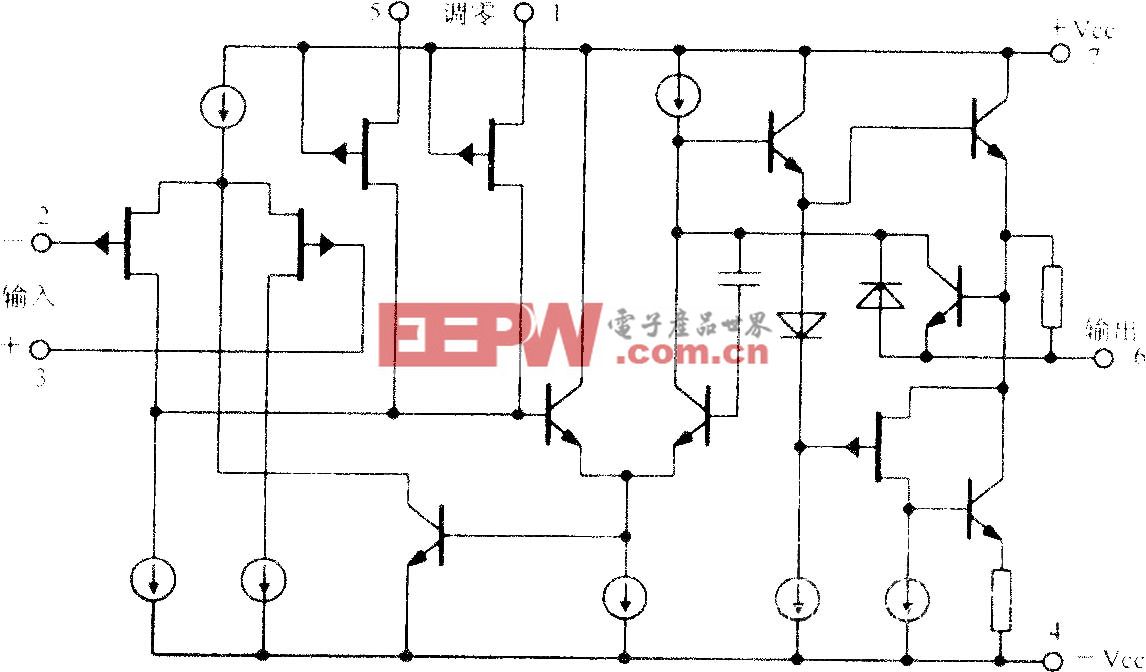

路D采用ADI公司锁相环

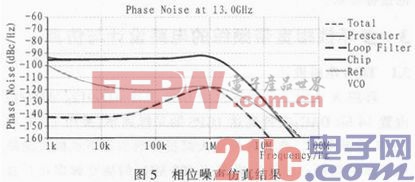

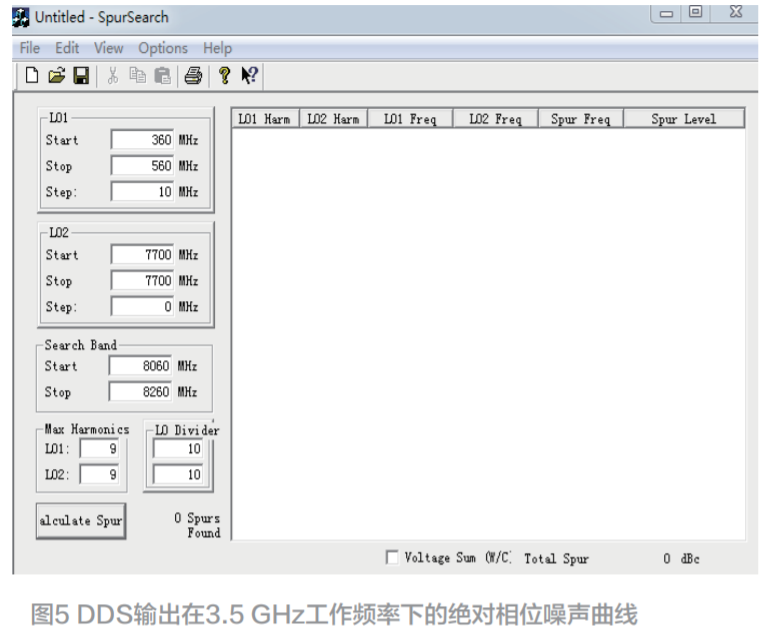

路D采用ADI公司锁相环 芯片AD4108。该芯片工作频率达8 GHz,控制简单、功耗极低,同时具有良好的噪声基底性能。经软件仿真,末级锁相环

芯片AD4108。该芯片工作频率达8 GHz,控制简单、功耗极低,同时具有良好的噪声基底性能。经软件仿真,末级锁相环 路电路参数及输出相噪如图4,5所示。

路电路参数及输出相噪如图4,5所示。

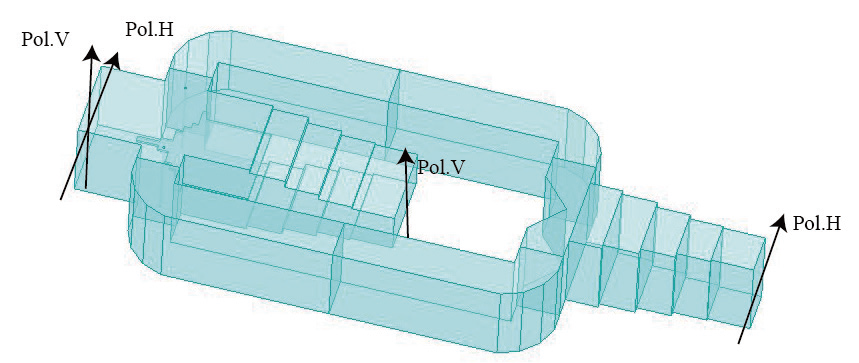

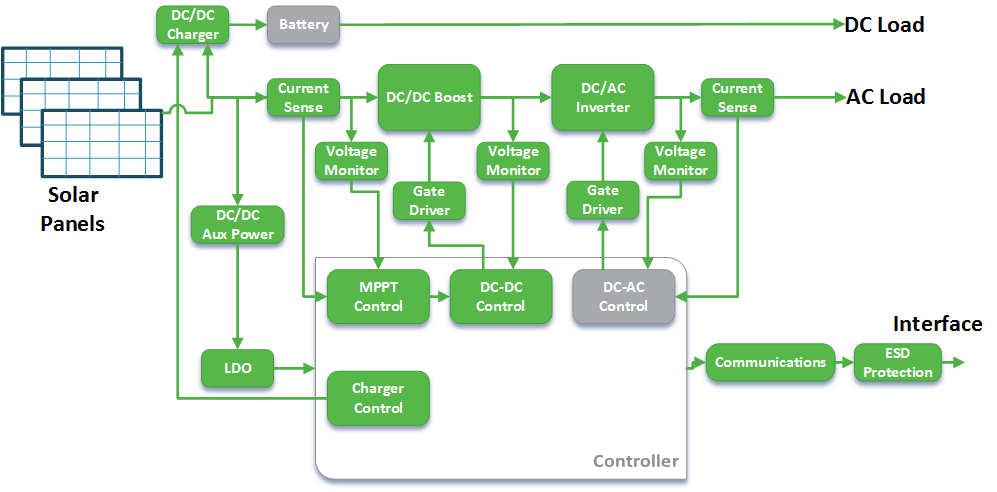

整个多环锁相电路结构比较复杂,包含锁相电路及数字控制电路等。为保证输出信号相位噪声和杂散抑制性能,结构设计中采取了多腔体分隔的结构,并注意微波吸收材料的使用,保证各个功能环路工作稳定且整体电磁兼容性能良好。

4 电路调试与测试结果

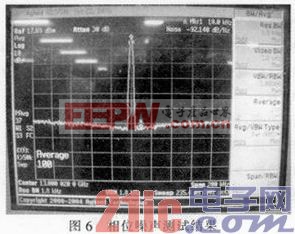

由于合理的方案设计和准确仿真,相位噪声等主要指标均可实现。如图6所示,全频段输出信号相位噪声可达到-92 dBc@1kHz;-92 dBc @10kHz。

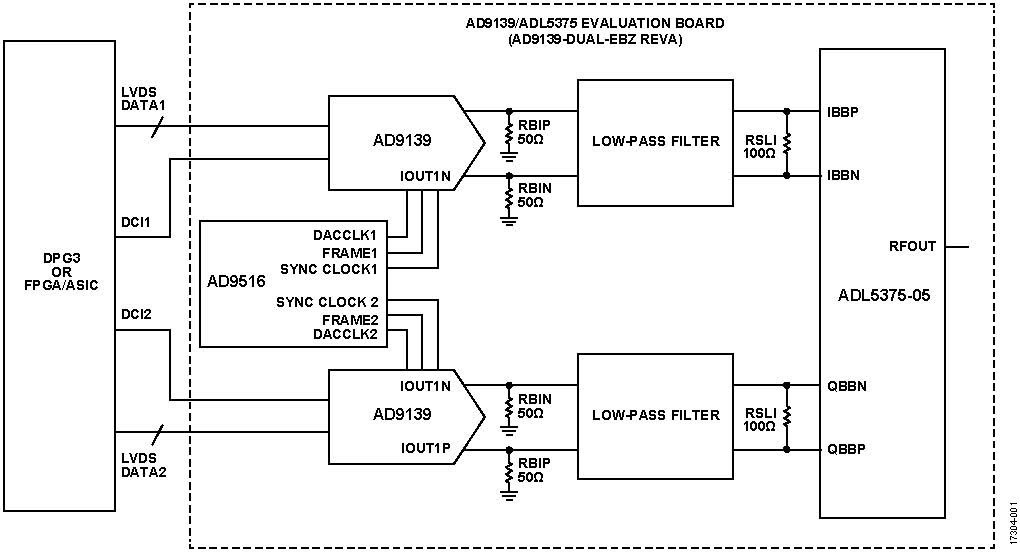

由于各功能环路输出中间频率信号较多,杂散控制是调试难点。在测试中发现,有少数频点的近端有杂散较大,主要分布在参考100 MHz整数倍附近的细步进频段,经分析,该类杂散的产生主要是由于环路A中DDS输出信号与参考信号100 MHz及其谐波经链路泄露或空间辐射进入混频器及鉴相器中,产生的高阶交调出现在输出信号近端,由于分布在锁相环 路带宽以内,难以消除。该现象的产生说明,多环锁相的细步进频综对模块内部各功能单元的电磁屏蔽与隔离要求非常高。通过调试分析,可通过改变A、C环路输出频率和环路D的倍频次数N的方法规避和解决。根据公式(2),通过扫频,一旦发现存在近端杂散的频率点,通过改变fDDS、fLO2和末级锁相环

路带宽以内,难以消除。该现象的产生说明,多环锁相的细步进频综对模块内部各功能单元的电磁屏蔽与隔离要求非常高。通过调试分析,可通过改变A、C环路输出频率和环路D的倍频次数N的方法规避和解决。根据公式(2),通过扫频,一旦发现存在近端杂散的频率点,通过改变fDDS、fLO2和末级锁相环 倍频次数N的频率组合,同样可以实现相同频率的输出,且fDDS发生改变,与100 MHz的高阶交调杂散分布远离主信号中心,可被末级锁相环路滤波器滤除。图7为经过后期频率控制程序处理前后的杂散分布对比图,可见主信号近端杂散已经明显消除。

倍频次数N的频率组合,同样可以实现相同频率的输出,且fDDS发生改变,与100 MHz的高阶交调杂散分布远离主信号中心,可被末级锁相环路滤波器滤除。图7为经过后期频率控制程序处理前后的杂散分布对比图,可见主信号近端杂散已经明显消除。

经不断调试改进,各项指标最终测试结果如表1,均满足设计指标要求。

5 结 论

文中介绍了基于多环结构的锁相宽带频率合成技术,在实现细频率步进和低杂散的指标要求情况下,相位噪声可达到≤-92 dBc/Hz@1 kHz,满足系统对高质量频率合成器的需求,具有较好的应用前景。

dc相关文章:dc是什么

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理 鉴相器相关文章:鉴相器原理 锁相环相关文章:锁相环原理 锁相放大器相关文章:锁相放大器原理

评论