一种适用于高速接口电路的新型均衡电路

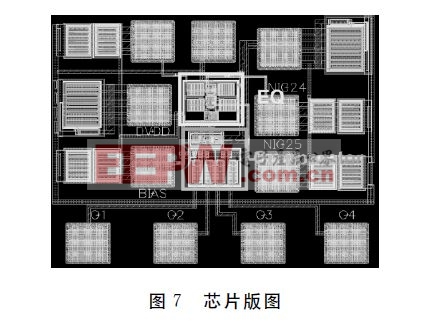

该电路最后使用0.13μm CMOS工艺实现,芯片面积约为0.26mm2,电路包括两级级联的均衡器,交叉耦合接比较器作为限幅放大器及后级驱动电路,后仿芯片功耗为34.7mW,芯片版图概貌如图7所示。

6 结束语

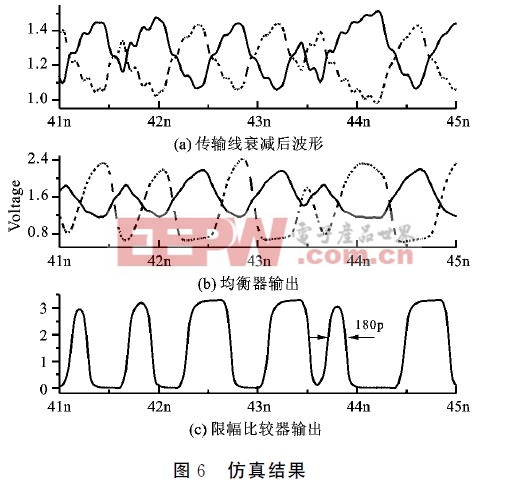

文中使用0.13μm CMOS实现了一款可以补偿高频信号传输线损耗的新型均衡器结构.仿真结果验证得到,该电路可以接收速率高达5Gbit/s数据信号,并对传输线损耗造成的高频衰减提供了有效的补偿.在设计中,使用了对称负载和有源电感等技术,避免了使用片上电感.对电路的噪声抑制和均衡效果起到了明显的促进.电路仿真使用Hspice,功耗仿真结果满足设计需求

电路相关文章:电路分析基础

评论