基于数字示波器的高精度抖动测试方法

从当前各种高速串行总线和数据链路的定时余量规范中表明,在整个数字系统中更加严格地控制抖动是必须的。只有全面有效的测试和分析抖动,其根本原因才能被隔离,从而针对引起系统抖动的原因来减少抖动,提高系统性能和稳定性。像PCI-Express、FBD、InfiniBand、SerialATA和 DVI等都对于时钟和数据抖动有明确要求。本文针对示波器进行的实时抖动测试方法,探讨了影响抖动测试结果的关键因素。

典型的抖动测试方法

为成功地设计高速数字系统,不仅需要理解什么是抖动,计算抖动的大小,还需要对不同的抖动分量进行隔离和分解,分析造成抖动的原因,进而避免在高速系统中出现抖动造成的系统故障。在了解抖动测试前,明智选择合适的抖动测试工具和方法成为整个抖动测试工作的第一步。目前有几种抖动测试工具可供选择,误码仪 (BERT)直接测试系统的误码率,但是价位昂贵,功能单一,不适合设计人员和调试人员;采用时间间隔分析仪测试抖动也存在功能单一,抖动分析能力不足的限制。高性能数字示波器成为当前最流行的抖动测试工具。

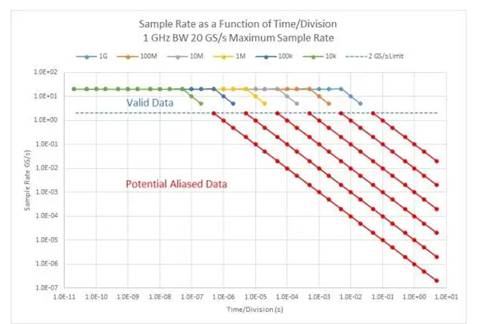

对于数字示波器而言,典型的抖动测试方法主要有2种:

1) 采用数字存储示波器的等效采样模式或直接使用采样示波器,通过直方图统计测量定时抖动。等效采样的缺点是无法消除示波器自身的触发抖动对测试结果的影响,并且由于它采用的是多次触发、多次采集、累计显示的工作方式,对于电路设计和调试而言受到较多的限制,无法进行深层的抖动分析。

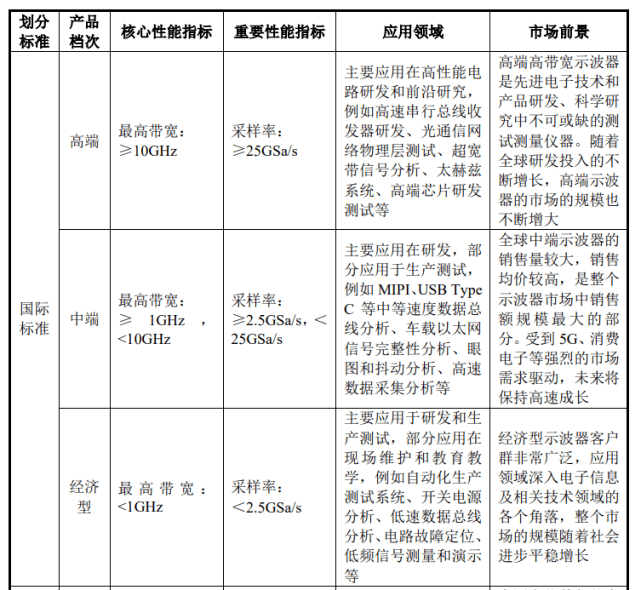

2) 更为流行的方法是采用数字存储示波器的实时捕获模式,单次触发,连续采集大量数据,配合相应的抖动测试软件进行抖动测试。对比于等效采样方法它消除由于示波器自身的触发抖动对测试结果造成的影响,并且能够进行复杂的抖动分析和抖动分解得到每一个抖动分量,帮助设计和测试人员分析抖动产生的原因,甚至通过抖动分解估算系统的误码率。例如,在美国国家信息标准委员会(INCITS)下属的T11.2组织在有关抖动和信号完整性方法论(MJSQ)中,推荐泰克实时示波器配合TDSJIT3抖动分析软件进行抖动测试和分析。图1是TDSJIT3实时抖动测试结果。

图1:TDSJIT3进行高速数据的抖动测试和分解。

抖动测试

抖动可以描述为相邻脉冲边沿、甚至非相邻脉冲边沿周期或相位的定时变化。这些指标适合检定长期和短期的时钟和数据稳定性。通过更加深入地分析抖动指标,利用抖动测试结果,预测复杂系统的数据传输性能。

周期抖动用来衡量时钟或数据周期样点的边沿到边沿定时。例如,通过测量1,000个时钟周期上升沿之间的时间,可以对统计的周期取样,统计数据会告诉您信号的质量。标准偏差变成RMS周期抖动,最大周期减去最小周期,得到峰到峰周期抖动。每个不同周期测量的精度决定着抖动测量的精度。

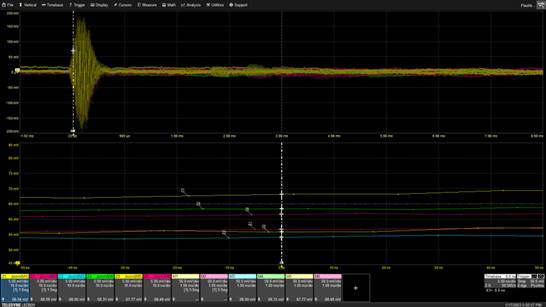

相位抖动用来衡量被测信号边沿相对于一个参考信号边沿的时间偏差,从而可以检测到信号相位中的任何变化。这一指标在许多方面不同于周期测量指标。第一,它单独使用每个边沿,而没有使用“period”或“cycle”一类的说法。第二,它可以测量大的时间位移。边沿相位可以偏离几百或几千度,但仍可以以非常高的精度进行测量(360度等于一个周期或循环时间)。测量相位误差常用的指标是时间间隔误差(TIE),测量结果用相对于度的秒来表示。TIE把信号边沿与参考边沿匹配起来,对各边沿之差相加计算总和。在比较了大量的边沿之后,可以为分析提供一个样点集合。与上面的周期测量一样,标准偏差变成RMS TIE,最大时间减最小时间得到峰到峰值TIE等等。TIE测试精度取决于构成样点集合的各个测量的精度。图2显示的是对一个时钟信号的不同抖动测试参数。

图2:典型的时钟信号抖动测试参数。

评论