使用Quartus II提高可编程逻辑设计效能的T.I.P.S

Altera

今天每一个工程人员都把精力放在效能上面,即用最少的资源做最多的事情。Altera的PLD开发软件平台工具Quartus II 能帮助工程人员提高效能,它是如何实现的呢?概括起来说就是 Quartus II的T.I.P.S.

• T代表Timequest, ——新一代ASIC功能时序分析仪,支持业界标准Synopsys设计约束(SDC)时序分析方法。

• I代表增量式编译(Incremental Compilation)支持自下而上的设计流程,可以分别建立和优化设计模块。系统体系结构可以逐步集成经过优化的设计模块,在整个集成过程中,保持设计模块的性能不变。

• P 代表PowerPlay功耗分析和优化技术:它能够对功耗进行自动优化,从设计概念形成到实施阶段,帮助您提高功耗管理的效率。

• S 代表SOPC Builder,它避免了繁杂而又容易出错的系统集成任务,帮助您迅速建立系统。

T: TimeQuest

TimeQuest时序分析仪应用于标准FPGA时序验证

新的、使用方便的TimeQuest时序分析器提供完整的GUI环境,建立约束和时序报告,并提供ASIC功能特性,自然地支持Synopsys设计约束(SDC)格式,以及全脚本功能。TimeQuest时序分析器是 65nm 器件和未来工艺技术的默认时序分析器。 Altera 的 Quartus® II 软件针对 65nm 和以前的设计继续提供标准时序分析器。

谁应该使用TimeQuest时序分析器

Altera建议在180nm、90nm和65nm工艺节点上所有新的Altera® 设计都使用 TimeQuest 时序分析器。此外,还建议所有移植到65nm器件上的设计都使用TimeQuest时序分析器。

注意: 移植到65nm器件上包括存储器接口 (DDR、DDR II等)的设计应使用TimeQuest时序分析器,而不要使用标准时序分析器。

和标准时序分析器相比,为什么要使用 TimeQuest 时序分析器

从基本的时序分析要求到高级时序分析要求,与标准时序分析器相比,TimeQuest时序分析器都有明显的优势。

• 基本时序分析要求—— TimeQuest 时序分析器提供使用方便的GUI,建立约束,查看时序报告。使用 TimeQuest 时序分析器,它提供和标准时序分析器相同的流程 ( 包括默认的时钟约束和 fMAX 报告 ) ,您不必再学习SDC或者其他的约束格式。而且,与标准时序分析器相比, TimeQuest 时序分析器提供更多的约束对话框,加速建立约束。

• 中间时序分析要求—— TimeQuest 时序分析器能够自然地支持 SDC 格式。 TimeQuest 时序分析器简化了 SDC 的学习过程,提供按需的交互式报告功能。 与 标准时序分析器相比, TimeQuest 时序分析器能够建立更精确的时序行为模型 ( 例如,上升 / 下降时序模型 ) 。 Hardcopy II 和 65nm 器件系列的性能可以提高 3-5 %。

• 高级时序要求—— TimeQuest 时序分析器提供全脚本功能,建立约束,生成报告,管理时序分析流程。 TimeQuest 时序分析器支持高级 (though- 支持 ) 报告,并且能够建立定制报告。 TimeQuest 时序分析器简化了对源同步接口 (DDR 、 DDR2) 的约束。而且, TimeQuest 对 SDC 的自然支持还能够轻松实现 ASIC 原型开发,或者移植为 Hardcopy 结构化 ASIC 。

{{分页}}

I: Incremental Compilation (增量式编译)

Quartus II 编译增强特性

高密度 FPGA 设计的性能和效能达到最佳

Quartus® II 软件首次实现了 FPGA 业界的渐进式编译功能,支持自上而下和自下而上基于团队的设计,缩短了设计迭代的编译时间,同时保持性能不变,使 Quartus II 软件成为高密度 FPGA 设计中效率最高的软件。使用 Quartus II 软件来进行高密度 FPGA 设计,您可以迅速完成设计。

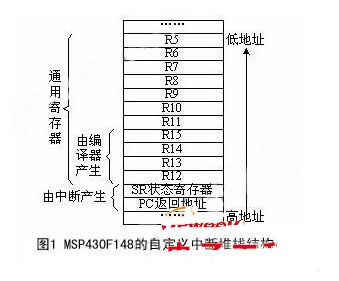

在系统集成过程中,保持设计模块的性能不变

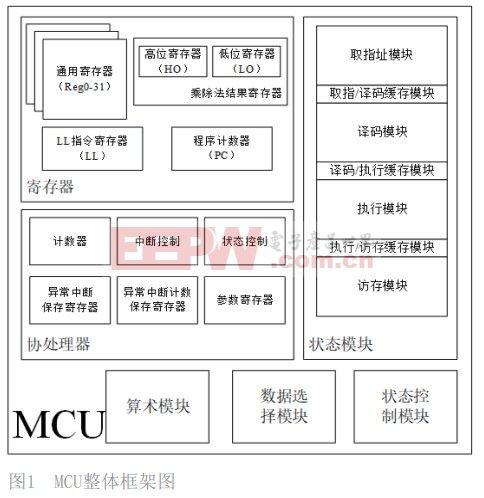

Quartus II 渐进式设计在功能上的改进包括了基于团队的工程管理流程,大大提高了团队设计的效率。系统规划人员可以首先采用自上而下的方法定义一个工程。在新的工程管理器界面中 ( 参见图 1) ,您可以生成所有的自下而上的设计分区工程,让每个工程师独立地进行开发和优化,然后将结果集成到整个设计中。在系统集成阶段,系统规划人员还可以对准备好的优化设计模块逐步进行集成,同时保持设计模块的性能不变。

图 1. 工程管理器 GUI

每天进行更多的迭代,实现最大效能

通过缩短编译时间 ( 参见图 2) ,您可以由原来的每天只能迭代一到两次提高到现在的四到十次,极大的提高了设计效能。

图 2. 缩短高密度 FPGA 设计的编译时间,进行更多的迭代

更快地达到时序逼进

渐进式编译功能使设计人员能够为综合和适配 / 逻辑布局确定物理和逻辑分区,如图 3 所示。

图 3. 渐进式编译的设计分区

Quartus II 软件在处理设计时,保留您指定的分区,使您能够优化特定分区而保持其他分区不变。高级优化技术会导致编译时间增加,而渐进式编译功能则使降低了这种影响,提高时序逼近性能,在特定设计分区上使用物理综合等高级优化技术,保持其他分区不变。

例如,如果顶部分区和 F 分区 ( 参见图 3) 已经达到性能要求,那么您可以只修改 B 分区或者打开物理综合功能,重新编译设计来进一步优化设计的总体性能。

使用方便

如图 4 所示,可以方便的在 Quartus II 软件工程导航器层次视图中分配分区。

图 4. 在用户界面中确定设计分区

完成设计分区后,设计人员通过为每个分区设置一个网表类型属性,实现对设计处理过程的高级控制。表 1 是一些有效的设置。

{{分页}}

P: PowerPlay功率分析和优化

Quartus II PowerPlay功率分析和优化技术

引入Quartus® II 的PowerPlay功率分析和优化技术后,Altera在软件技术上领先的传统,得到了进一步的巩固。PowerPlay技术可以使您对动态和静态功耗进行精确的分析和优化。在2005年即将发布的Quartus II新版本中,PowerPlay功率分析工具能够满足速度和面积的要求,提供按键式静态和动态功耗优化。

从设计概念产生到实施过程中的功率分析

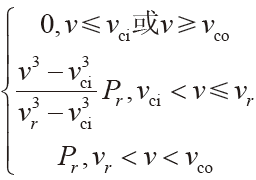

Quartus II PowerPlay功率分析工具使您能够在早期设计概念产生到设计实施阶段过程中对功耗进行估算,如图2所示。

图2. PowerPlay功率分析

PowerPlay早期功率估算器

设计人员可以在设计概念产生阶段利用PowerPlay早期功率估算器表单对静态和动态功耗进行估算。利用新的Quartus II PowerPlay功率分析器功能,能够在设计实施阶段对功率进行精确估算。

PowerPlay功率分析器

Quartus II软件现在具有PowerPlay功率分析器功能,通过早期功率估算器表单,该功能提高了功耗估算的精度。该表单:

• 考虑器件资源使用和布局布线结果

• 考虑功能和时序仿真输入/输出激励

• 当仿真矢量输入无效时,对预期的设计节点工作速率进行统计分析

Quartus II PowerPlay功率分析器生产详细的报告,指明哪种器件结构甚至是设计层次模块消耗了最大的热量。图3列出了PowerPlay功率分析器报告。Quartus II用户现在可以利用这些报告结果,优化设计,实现低功耗目标。

图3. PowerPlay功率分析器报告表

S: SOPC Builder

SOPC Builder起到什么作用?

在建立一个系统时,最耗时的任务是根据系统要求集成大量的组件。SOPC Builder避免了手动系统集成任务,使您能够将精力集中在定制用户逻辑设计上,从而突出系统优势。 Altera® Quartus II 设计软件的所有版本均包括SOPC Builder 系统生成工具。SOPC Builder具有:

• 使用方便的 GUI 接口,帮助用户高效地建立并修改系统。

• 自动集成常用的 SOPC Builder 组件、Altera知识产权 (IP)、Altera宏功能合作伙伴计划 (AMPPSM) IP,以及定制组件内核等。

• 您可以高效地连接外部处理器和SOPC Builder可用IP库,包括Serial RapidIO™、千兆以太网、PCI和PCI Express。

• 在您的系统中建立自己的可重用定制组件。

• 生成系统 HDL,包括针对系统组件集成需求而经过优化的系统互联架构。

迅速推向市场——SOPC Builder应用

您可以在全部或者部分FPGA以及MAX® II CPLD 系统设计中使用SOPC Builder。采用SOPC Builder接口来选择元件,以及元件间的连接,您会发现系统集成任务能够在几分钟内完成。公共SOPC Builder应用包括:

• 构建定制Nios® II 嵌入式处理器解决方案

• 采用外设扩展定制单机处理器

• 通过PCI接口连接至ASSP以及CPU

• 构建数字信号处理(DSP)协处理器

{{分页}}

定制Nios II嵌入式处理器解决方案

现在,您使用SOPC Builder和Altera Nios II处理器定义一个定制处理器方案,来轻松满足您的需要(参见图1)。

图1. 定制Nios II嵌入式处理器解决方案

单机处理器外设扩展

采用SOPC Builder元件编辑器功能,您可以轻松实现几乎所有外部处理器以及数字信号处理器(DSP)的接口(参见图2)。在产生处理器的SOPC Builder元件接口时,您只需点击几次鼠标,便可以加入其他I/O引脚、预封装外设以及自己的定制外设。SOPC Builder将会为您的软件开发小组构建系统,输出头文件。开发小组可以采用其常用的集成开发环境(IDE),通过外部处理器来访问外设。

图2. CPU外设扩展

参见如何轻松实现单机处理器外设扩展:

• SOPC Builder在线演示

通过PCI连接至ASSP以及CPU

多种ASSP和处理器含有PCI接口。如果您使用Altera SOPC Builder和SOPC Builder Ready PCI MegaCore®编译器,您将会轻松构建通过PCI实现与这些ASSP以及外部处理器进行通信的系统(参见图3)。

图3. PCI接口实现的ASSP以及CPU连接

DSP 协处理器

您采用SOPC Builder可以轻松构建DSP协处理器,分担DSP器件的任务。您还可以利用Altera FPGA并行DSP处理能力,提升系统DSP处理性能。SOPC Builder元件编辑器将会帮助您构建德州仪器(TI)DSP处理器外部存储器接口(EMIF),或者其他外设扩展以及其他处理器的外部存储器接口(参见图4)。

图4. DSP协处理器

{{分页}}

SOPC Builder接口

SOPC Builder直观的用户界面使您能够轻松的选择元件,进行参数赋值,选择元件间的连接,生成包括互连在内的完整系统,自动生成方便软件工程师使用的存储器映射头文件(参见图5)。

图5. SOPC Builder用户界面

总结:最好的感受Quartus II T.I.P.S的方法就是立即安装,相关的资源如下。

最新Quartus II软件免费下载:

Quartus II 开发软件7.1文档:

另外,说到TIPS, ”Show me, Guide me, Test me”, 是一个集成在Quartus II中非常好的学习工具,它可以在安装完Quartus II 软件后,HELP菜单中TUTORIAL栏里获得。

评论