嵌入式逻辑分析仪在FPGA时序匹配设计中的应用(07-100)

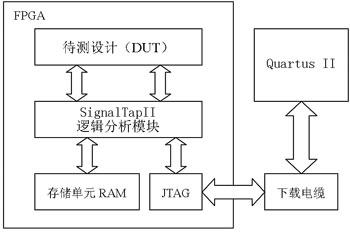

根据理论计算,一个D触发器会带来一个clk156的时钟的延时,那么要延时9个clk38的时钟必须使用36个D触发器。实际上,D触发器固定的建立时间、保持时间,也会带来系统延时。根据Signal Tap II采集的波形对D触发器的个数进行适当的删减,达到了精确的9个clk38时钟的延时,最后的时序匹配模块由34个D触发器构成。

本文引用地址:http://www.amcfsurvey.com/article/81757.htm 图6为时序匹配模块的内部框图。D触发器D端口接flag,clk端口接clk156,第30个和第34个D触发器Q端口分别连接Flag_delay8和flag_delay9。该时序匹配模块采用四倍于clk38的clk156作为驱动时钟,以确保延时信号的相位延时足够精确。

图7为Signal Tap II采集时序匹配模块的波形输出。其采样时钟为38MHz,采样深度为4K bit。rgb_regroup_output[23..0]为位面分离后红色输出的数据。可以看出,输出数据在flag_delay9的上升沿开始由FFh(高阻)变成有效数据00h,达到了数据和控制信号的完全同步。

性能分析

把该时序匹配模块加入工程,重新综合布局布线,下载到全彩LED大屏同步显示控制系统的接收板上,Quartus II编译报告中除了占用部分内部存储器资源和LE资源,其它的(如I/O引脚的利用率)都没有变化。观察LED大屏显示效果,图像清晰稳定,证明了该时序匹配模块的可行性。

该时序匹配模块仅为LED同步显示控制系统中一个最简单的模块,用于示例说明嵌入式逻辑分析仪Signal Tap II在FPGA时序匹配设计中的应用方法。应用Signal Tap II还能解决各种各样的问题,如外部存储器的双向数据口的实时波形检测、驱动模块的并串转换波形等。使用Signal Tap II有如下优点:

·不占用额外的I/O引脚。利用Signal Tap II成功的采集了FPGA内部信号的波形,如flag,flag_delay8,flag_delay9等都为FPGA内部寄存器信号。

·Signal Tap II为硬件板级调试工具,它采集的波形是工程下载后的实时波形,方便设计者查找引起设计缺陷的原因。

·节约成本。Signal Tap II集成在Quartus II软件中,无需另外付费。

评论