基于MPC8260和FPGA的DMA接口设计

2.1.2 中断处理

本文引用地址:http://www.amcfsurvey.com/article/82690.htm系统设计中使用了两类中断方式: IRQ引脚引入的外部中断和CPM触发的内部中断。初始化过程包括:使能对应的中断屏蔽位、选择中断优先级、连接对应中断向量号和中断服务程序等。为了保证较好的传输实时性,需要把中断优先级尽量设得高一些。

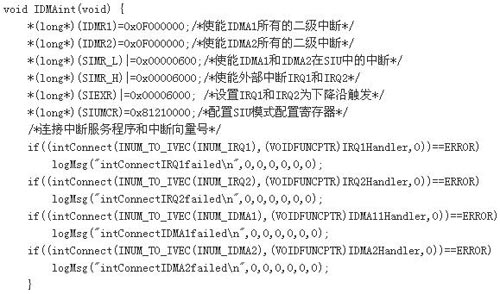

与一般中断处理过程的区别在于:MPC8260中断处理控制器采用分级结构来扩展中断信号总数。CPM内的中断就是二级中断,需要通过CPM中断控制器和SIU中断控制器两级中断控制。本设计中用来通知内核本次传输过程结束的中断是CPM内最后一个BD表传送结束的信号BC(BD Completed)。BC信号和命令结束等几个信号一起通过SIU中断挂起寄存器中的IDMA位向内核发出中断信号。所以在中断初始化时要同时有效IDMA屏蔽寄存器和SIU中断屏蔽寄存器对应的比特位。具体的中断初始化实例如下:

尤其要注意的是,中断处理程序结束之前的清SIU中断挂起寄存器,不能直接在SIU中断挂起寄存器的IDMA位写1,而是要通过在IDMA事件寄存器的BC位写1来间接地清SIU中断挂起寄存器。

2.2 FPGA部分程序

系统中的FPGA芯片选用Xilinx公司的VirtexII 3000。利用VirtexII内嵌的大容量BlockRAM配置为单口RAM来做缓冲区,在程序中可以用Xilinx的集成开发环境ISE 7.1i内部自带的IP核生成。对FPGA来说,由于数据的输入/输出都是顺序的,所以两端都只要1根地址线用于区分相邻的两个数据就可以了。地址线配合内部计数器构成读写指针,当写指针从缓冲区的一半跳到另外一半时发相应的中断信号。

FPGA设计的关键部分是和MPC8260的总线接口设计。通过适当选择缓冲区的起始地址和长度,可以使MPC8260读FPGA都以突发的方式进行。设计中,MPC8260对FPGA的突发读写遵循自己配置的UPM模式,所以要综合考虑UPM模式设计和FPGA读写逻辑设计。在设计UPM模式时,可以在每次MPC8260锁定数据总线数据之前由通用功能信号线(General Purpose Line,GPL)产生一个下降沿通知FPGA往数据总线上写新数据;或者通过GPL把总线时钟送到FPGA达到收发同步来完成MPC8260与FPGA之间的读写。

3 总结

结合MPC8260的中断处理和IDMA传输机制,设计了一种MPC8260和FPGA之间的高速数据传输接口。测试结果显示:采用循环读的方式把FPGA中的数据复制到SDRAM中,数据传输速率只有11 Mbps左右;而采用本文介绍的IDMA方式,最高速率能够达到500 Mbps,并且内核占用率较低,实验结果完全能够满足系统设计需求。本研究对于PowerPC系列CPU的接口设计有一定的参考价值。

参考文献

[1] Freescale. MPC8260 PowerQUICCTM II Family Reference Manual .MPC8260RM Rev.2, 2005-12.

[2] Freescale. MPC8260 PowerQUICCTM II IDMA Functionality.Rev. 3,2006-02.

[3] Freescale. MPC8260 IDMA Timing Diagrams. Rev. 4,2006-07.

评论