采用West Bridge架构提升系统性能、缩短开发周期、并降低便携式消费类电子产品的成本(08-100)

West Bridge Astoria具有三个接口:一个处理器“P”端口、一个高速USB“U”端口,以及一个海量存储“S”端口。“P”端口支持嵌入式处理器连接,同时还支持硬件 DMA 存取。Astoria采用灵活而可配置的“P”端口,可支持不同处理器上的各种标准接口。“U”端口提供USB2.0高速USB链接,“S”端口经配置后能够支持各种海量存储器件,如 SD/SDHC、SDIO、MMC、CE-ATA以及SLC/MLC NAND 等。

本文引用地址:http://www.amcfsurvey.com/article/91683.htm图1中的红色箭头显示了三个端口之间可能的数据路径,其中所采用的是 West Bridge Astoria实现了革命性突破的至独立多媒体的同时链接 (SLIM) 架构。该 SLIM构架使所有三个数据路径能够同时运行,从而实现海量存储与外设功能的多任务执行。

支持最新标准

如前所述,当前市场上的嵌入式处理器不能为最新的海量存储和外设标准提供足够的支持,有时甚至完全不能支持。West Bridge 能支持 USB 2.0 高速等最新的外设连接标准,此外还支持 SLC/MLC NAND、SD2.0 SDHC/SDIO、MMC4.2 以及 CE-ATA 等新型海量存储器件。West Bridge器件的设计周期也大大比完全成熟的处理器设计周期要短。因此,我们可以预见,就像 PC 领域的南桥、北桥一样,West Bridge 将成为嵌入式系统的必需的处理器,来支持最新的技术标准。

优化的高速USB与海量存储性能

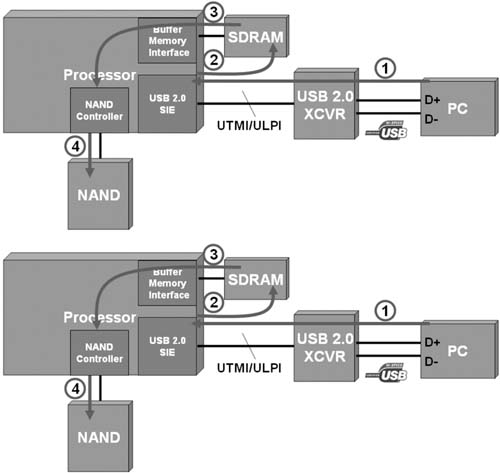

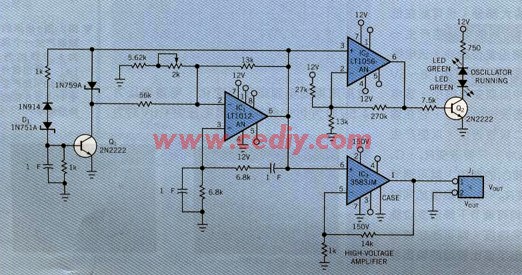

图 2 显示了 USB 2.0 高速实施方案的典型示例,其中的嵌入式处理器集成了高速 USB SIE 与外部收发器。从PC传出的数据首先穿过高速USB2.0信号高速管道,并缓冲至 SDRAM 中。处理器随后从SDRAM读取数据,并写入海量存储设备。这一系列中间传输机制不仅会防碍系统充分发挥高速USB的性能,而且还会在软件未经认真优化的情况下显著拖慢整体系统速度。因此,采用这种架构通常不能获得最佳的消费者使用体验。

图 2 带集成高速 USB 控制器的系统数据流程

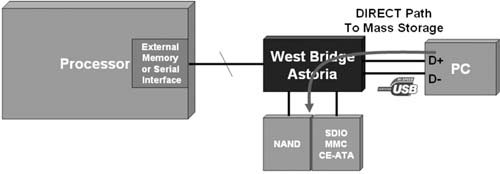

与图2所示的架构不同,图3显示的West Bridge架构能够直接将存储器件连接至West Bridge。数据传输完全不会占用处理器资源,因为处理器不再位于数据路径上,从而让处理器留下更多的带宽,使处理器能够拥有更多的资源来处理更重要的任务。

图3 采用West Bridge实现的从PC到海量存储单元的直接数据路径

评论