利用频域时钟抖动分析加快设计验证过程(07-100)

—— 利用频域时钟抖动分析加快设计验证过程

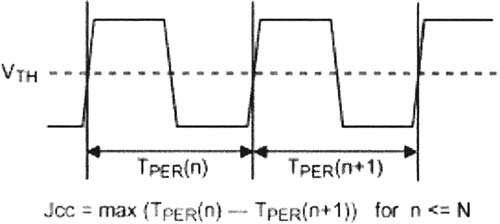

参考时钟是最终的系统定时源。它为发射机、已分配和未分配的时钟系统提供时基,而接收机的时钟恢复电路可以重现参考时钟特征。现在我们将探讨时钟抖动如何在系统发射机中进行传输。

发射机必须用适当的因数乘以参考时钟获得数据速率,才能确定逻辑变换定时。例如,对于100 MHz参考时钟和5 Gb/s输出信号,发射机将用PLL给参考时钟乘以因数50。PLL乘法器不仅放大时钟抖动,还引入其自身的抖动,主要是PLL压控振荡器(VCO)的RJ。频率乘以因数n的结果是相位噪声功率载波比乘以n2,所以抖动迅速变大。

图2 发射机时钟抖动的结果

发射机中的PLL乘法器具有一定的频率响应,通常是如图3所示的二阶响应。非均匀频率响应会产生一个值得注意的问题:时钟抖动实际上有什么影响?如果PLL非常出色且带宽为零,那么它将过滤掉所有的时钟抖动,而为发射机提供无抖动时基。当然,零带宽意味着无限锁定时间,所以我们不得不综合考虑,但是PLL带宽越窄,参考时钟加入数据中的抖动就越小。确定时钟是否能在系统中正常工作且符合预期的BER要求,需要对抖动频谱进行详细测试。

评论