基于FPGA的多通道校准算法同步实现

FPGA实现

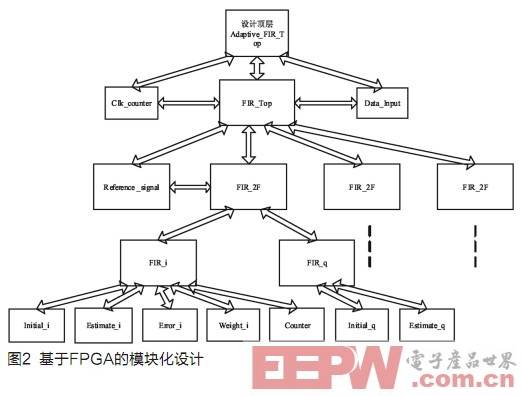

本文引用地址:http://www.amcfsurvey.com/article/96056.htm在本设计中应该综合考虑各方面因素,选择一种最佳模块结构和模块规模。本设计中的结构化层次是由一个顶层模块和若干个子模块组成,每个子模块根据需要再包含自己的子模块,以此类推,共5层,如图2所示。

本设计中,整个通道失配校准模块共需要90个乘法器。这些乘法器如果采用FPGA的逻辑资源直接构建,不仅难以保证理想的运算速度,而且硬件开销非常巨大。而FPGA芯片内部已经集成了18×18位的硬件乘法器模块,其速度快,实现简单,能有效节省FPGA的逻辑资源。由于系统设计时选用的FPGA芯片型号为Xilinx公司的xc2v8000ff1152-5,它集成了几百个硬件乘法器,因此可以全部使用硬件乘法器来完成相应的乘法运算。

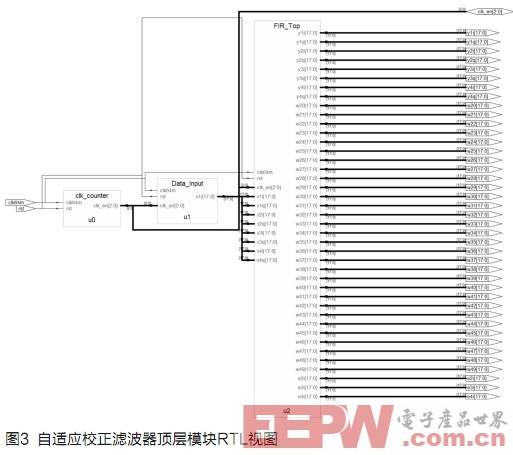

采用VHDL语言编写实现程序,开发环境为ISE 8.2i,综合工具为Synplify Pro v8.1,仿真工具为ModelSim SE 6.3f。图3所示的是程序经Synplify Pro v8.1综合后得到的LMS自适应校正滤波器顶层模块RTL视图。RTL视图即寄存器传输级视图,该图高度抽象为模块化结构,它是在对源代码编译后再现设计的寄存器传输级原理图。

所有算法模块均在全局使能信号clk_en不同状态的控制下进行工作,从而使算法运行达到8M周期,直至找到最佳权值,最终完成多通道校准的任务,实现多个通道的幅相一致性。

功分器相关文章:功分器原理

评论