学习AVR 系统时钟和时钟选项

作者:dolphin

时间:2012-10-31

时钟的设计,因系统的复杂度、集成度、速度的提高,越来越成为嵌入式系统设计的一个难题,所以多了解一些时钟的知识,对于整个系统的设计都是有所裨益的。

时钟系统及其分布

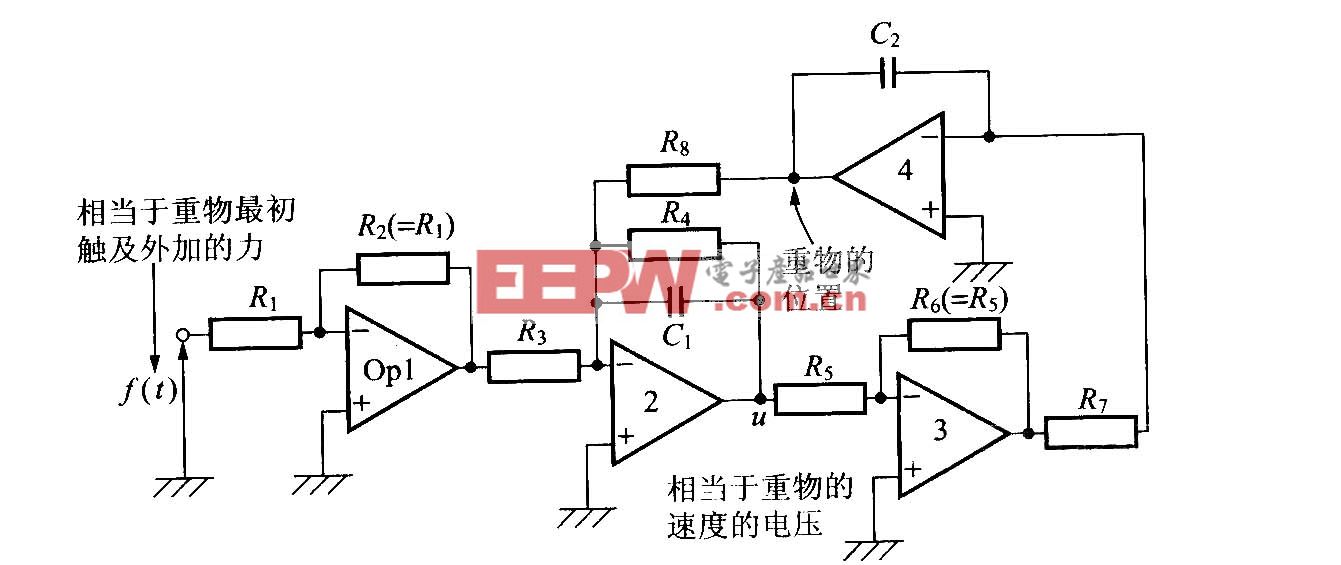

图 11 所示为 AVR 中的主要时钟系统及其分布情况。在任一给定时间,并不需要这些时钟都是活动的。为了减少功耗,可以由各种休眠模式来停止到某模块的时钟,如后面要学到的“功率管理和休眠模式”。下面将详细讲解时钟系统。

(罗亩按:自从功耗成为一个问题,计算机就学会了休眠;或者反之,仿生吧)

图 11. 时钟分布

CPU 时钟--C clkCPU

CPU 时钟被引入到与 AVR 内核操作有关的系统部分。这种模块的例子是通用寄存器堆、状态寄存器和存储堆栈指针的数据存储器。中止 CPU 时钟,将禁止内核的操作和计算。

I/O 时钟--C clkI/O

I/O时钟被大部分 I/O模块使用,如定时/计数器和 USART。外部中断模块也使用 I/O 时钟,但要注意一些外部中断是由异步逻辑检测的,即使 I/O 时钟被中止,这样的中断也可以被检测到。还有一个问题就是当 clkI/O 中止时,

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码