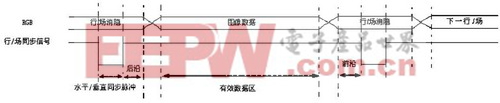

- 基于FPGA及DSP Builder的VGA接口时序和系统设计,本文基于DSP Builder的VGA接口设计方法,对VGA接口时序和系统设计需求进行了介绍,并在硬件平台下实现一维与二维信号的显示。

VGA接口标准

VGA显像原理

显示器通过光栅扫描的方式,电子束在显示屏幕上

- 关键字:

时序 系统 设计 接口 VGA FPGA DSP Builder 基于

- 书上看到的毕竟是理论的东西,实际应用中总会碰上意外的或者说是不可预测的情况,与其在那瞎推理,还不如动手做点实际的工作。 特权同学用的是11.0592MHz的STC89C52做测试,C代码也很简单: #include #d

- 关键字:

时序 实验 读写 RAM 扩展 单片机

- 在高速数字视频系统应用中,使用大容量存储器实现数据缓存是一个必不可少的环节。SDRAM就是经常用到的一种存储器。但是,在主芯片与SDRAM之间产生的时序抖动问题阻碍了产品的大规模生产。在数字电视接收机的生产实际

- 关键字:

控制 分析 时序 SDRAM 视频系统 嵌入式

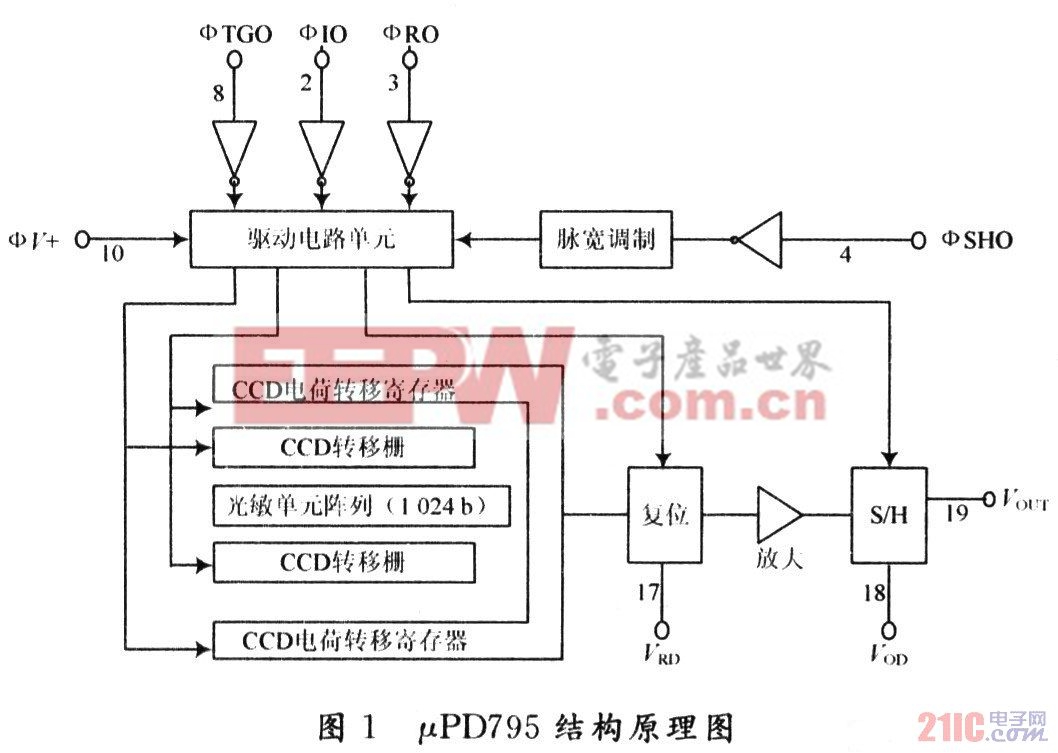

- 1mu;PD795结构原理及驱动时序1.1 mu;PD795结构原理mu;PD795是NEC公司生产的高灵敏度、低暗电流、具有内置放大电路和采样保持电路的线阵CCD图像传感器。它内部包含一列1 024像元的光敏二极管和两列525位的电荷转移

- 关键字:

时序 驱动 原理 结构 PD795

- 用GAL配合ISA总线模拟I2C总线时序实现对FI1256MK2的编程,FI1200 MK2系列电视信号前端处理器是飞利浦公司专为计算机多媒体环境下的射频应用而设计的。FI1256 MK2是该系列中的一个型号,它体积小,结构紧凑,性能稳定,可直接从射频信号解调出视频信号和音频信号,且只需单一

- 关键字:

总线 实现 FI1256MK2 编程 时序 模拟 配合 ISA GAL I2C

- 本文所设计的可适应于多种时序情况的DMA控制器,被应用于该图像协处理器之中后,能够很好地解决问题。 1 图 ...

- 关键字:

时序 DMA 控制器

- 过去十年中,高速数字总线已经获得了令人瞩目的发展,它们不仅比以往更快,而且还正在改变系统定时数据的方式。为提高数据吞吐量,新兴的同步数字总线可以通过一套定时机制在每个时钟周期内多次发送数据。本文将对源

- 关键字:

高速接口 时序

- 更高速的 ADC 在转换器输出和接收机输入之间有严格的时序要求;知道如何利用产品说明书数字来保证无错误数字 ...

- 关键字:

高速ADC 时序

- 一般来说,LCD 模块的控制都是通过 MCU 对 LCD 模块的内部寄存器、显存进行操作来最终完成的;在此我们设计了三个基本的时序控制程序,分别是: 写寄存器函数(LCD_RegWrite) 数据写函数(LCD_DataWrite) 数据

- 关键字:

驱动 设计 底层 时序 单片机 LCD 基于

- 更好、更强、更快。对于某些人来说,这个词可能唤起他们对20世纪70年代美国电视剧《无敌金刚》(TheSixMilli...

- 关键字:

Magma 时序 ECO QCP

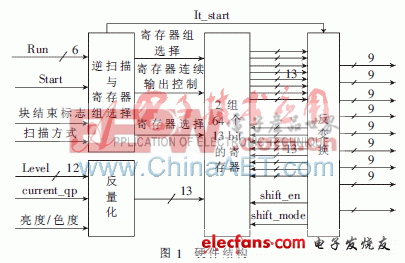

- RAM读写时序限制解决方案,本文为了提高AVS解码器的处理速度,综合了国内外学者的设计思想提出了一种逆扫描、反量化与反变换模块结构,在消耗逻辑资源允许的情况下提高了处理速度,做到速度和面积的平衡。 本文将逆扫描、反量化和反变换模块

- 关键字:

解决方案 限制 时序 读写 RAM

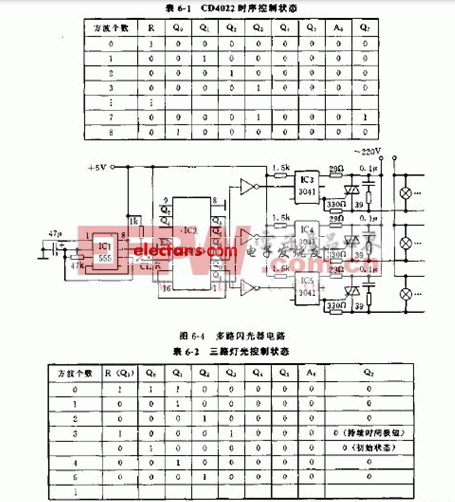

- 电路原理:电路中由IC1555于47UF电容器三路输出,CD4022工作原理是:在EN脚接地,CL脚输入方波脉冲,R脚为零电平情况下,设芯片的初始输出为Q7Q6Q5Q4Q3Q2Q1Q0=0 0 0 0 0 0 0 1,则输出将随方波脉冲做表6-1所示的变化

- 关键字:

电路设计 状态 时序 电路 闪光

- 80C51单片机的上电复位POR(Power On Reset)实质上就是上电延时复位,也就是在上电延时期间把单片机锁定在复位状态上。为什么在每次单片机接通电源时,都需要加入一定的延迟时间呢?分析如下。1 上电复位时序 在

- 关键字:

复位 时序 分析 延时 80C51 上电 单片机

- 单片机内部的时序

单片机执行各种操作时,CPU都是严格按照规定的时间顺序完成相关的工作,这种时间上的先后顺序成为时序。

单周期指令的操作时序

双周期指令的操作时序

时钟电路

时钟电路参数:

频

- 关键字:

时序 内部 单片机

- EMCCD ( E lectr on Mult iply ing Charg e Co upledDevice) 是新一代高质量微光成像器件。与传统CCD( Charg e Coupled Device) 相比, 它采用了片上电子增益技术, 利用片上增益寄存器使图像信息在电子转移

- 关键字:

驱动 电路 设计 方法 时序 CCD97 EM CCD 图像 传感器

时序介绍

您好,目前还没有人创建词条时序!

欢迎您创建该词条,阐述对时序的理解,并与今后在此搜索时序的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473