- 介绍一种采用单片SRAM和FPGA实现红外图像显示的新方案,并对显示系统结构、FPGA各功能模块设计、SRAM的读/写时序设计进行了详细论述。该图像显示方案可用于红外图像处理系统的硬件调试和红外图像处理效果观测。

- 关键字:

红外图像显示 SRAM FPGA

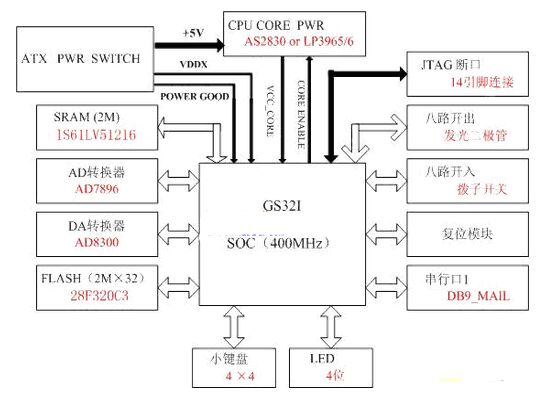

- 一. 引言 目前,嵌入式系统已经渗透到各个领域:工业控制,军事国防,消费类电子产品,网络通信等,但大部分领域的应用都是基于国外各大厂商的嵌入式处理器。在嵌入式领域使用国产芯片,走国产化道路已经成为一个迫切需要解决的问题。目前国内的芯片主要有星光系列、汉芯系列、神威系列、青鸟嵌入式芯片、方舟系列、龙芯系列等,这些芯片各有自己的特点。 本设计采用了龙芯系列的GS32I SoC处理器,探讨并设计如何构造一个小型嵌入式硬件系统,同时兼顾科研与应用两方面的要求,在该平台的基础上可以连接各

- 关键字:

GS32I SRAM

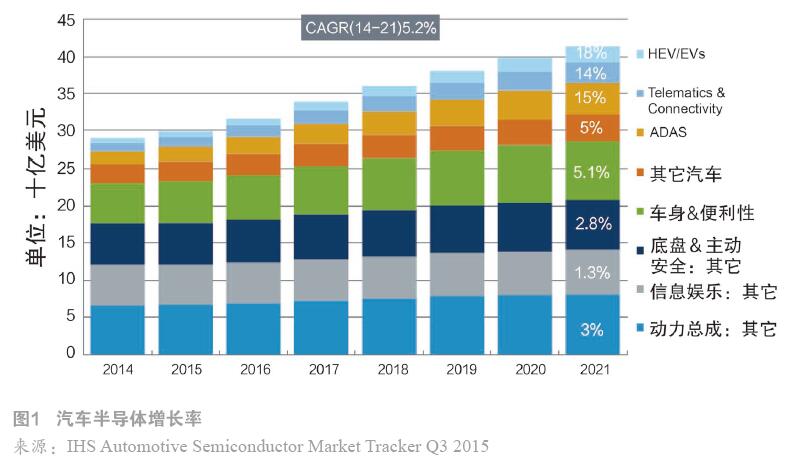

- 在“2017慕尼黑上海电子展”前夕的“汽车技术日”上,ISSI技术市场经理田步严介绍了车用存储器市场,包括:信息娱乐、ADAS、仪表总成、connectivity telematics四大类。

- 关键字:

汽车 SRAM DRAM SDRAM e.MMC 201704

- 在本系列第二部分,我们探讨了总线转换、总线翻转、地址奇偶校验等重要的总线问题。在第三也是最后一部分,我们将探讨校正问题,其中包括矫正训练、控制/地址信号校正和读写校正,以及纠错码(ECC)和QDR-IV存储器控制器的设计建议。 校正训练序列 存储器控制器和QDR IV较高的工作频率意味着数据有效窗口很窄。QDR-IV器件支持“校正训练序列”,它可通过减少字节通道之间的偏差扩大这个窗口,从而在控制器读取存储器的数据时,增加时序余量。校正训练序列是赛普拉斯的QDR-IV SRAM的

- 关键字:

QDR-IV SRAM

- 总线转换的注意事项 总线转换时间非常重要,其决定了读和写指令间是否需要额外的间隔来避免在同一个I/O 端口上发生总线冲突。 想象下QDR-IV HP SRAM 中端口A 先后收到写指令和读指令。从CK 信号的上升沿(与初始化写指令周期相对应)算起,在整整三个时钟周期后向DQA 引脚提供写数据。读数据则将在下一个周期发送,因为 DQ从CK 信号的上升沿(与初始化读指令的周期相应)算起五个时钟周期后才能获得数据。

- 关键字:

QDR-IV SRAM

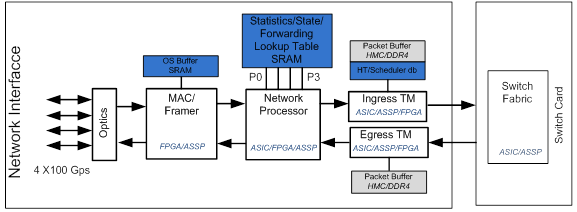

- 流媒体视频、云服务和移动数据推动了全球网络流量的持续增长。为了支持这种增长,网络系统必须提供更快的线路速率和每秒处理数百万个数据包的性能。在网络系统中,数据包的到达顺序是随机的,且每个数据包的处理需要好几个存储动作。数据包流量需要每秒钟访问数亿万次存储器,才能在转发表中找到路径或完成数据统计。 数据包速率与随机存储器访问速率成正比。如今的网络设备需要具有很高的随机访问速率(RTR)性能和高带宽才能跟上如今高速增长的网络流量。其中,RTR是衡量存储器可以执行的完全随机存储(读或写)的次数,即随机存储速

- 关键字:

QDR-IV SRAM

- 在过去40年里,随着制造工艺的进步,各种专用存储设备不断推向市场,满足着不同系统的存储需求。众多的选择,意味着系统架构师和设计者可以同时考虑多种方案,根据应用选择合适的存储子系统。尤其是在网络应用方面,架构师面临着不断增加的网络流量所带来的挑战。 据估计,2015年到2020年期间,网络流量的年均复合增长率(CAGR)将达到22%,这一增长主要来自于无线设备的爆炸式增长以及不断增加的视频用量。由于数据包处理的随机性,网络传输的关键—路由器和交换机的性能将和所使用的存储子系统的随机存取性能(以随机存取

- 关键字:

MAC SRAM

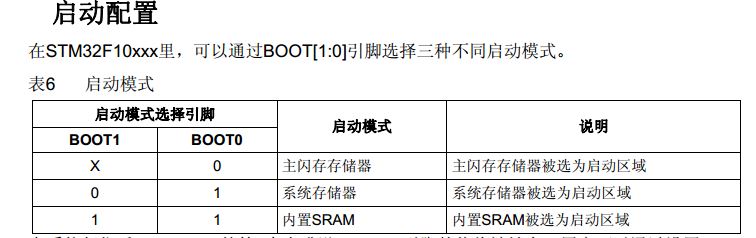

- STM32的基本系统主要涉及下面几个部分: 一、电源 1)、无论是否使用模拟部分和AD部分,MCU外围出去VCC和GND,VDDA、VSSA、Vref(如果封装有该引脚)都必需要连接,不可悬空; 2)、对于每组对应的VDD和GND都应至少放置一个104的陶瓷电容用于滤波,并接该电容应放置尽量靠近MCU; 3)、用万用表测试供电电压是否正确。调试时最好用数字电源供电,以便过压或过流烧坏板子。电压最好一步一步从进线端测试到芯片供电端。 二、复位、启动选择 1)、Boot引脚与JTAG无

- 关键字:

STM32 SRAM

- 针对嵌入式系统的低功耗要求,采用位线分割结构和存储阵列分块译码结构,完成了64 kb低功耗SRAM模块的设计。

- 关键字:

SRAM DBL 64 kb

- 由于SDRAM本身就是一个比较复杂的东西,之前小墨在学这方面东西的时候感觉很是吃力,于是那时候便暂时放下了,知道年后这段时间,小墨又重新拾起这个知识点,想要一口气把它调通了,再往下看其他的东西。学SDRAM,理

- 关键字:

fpga sram

- 具有片上错误校正代码的低功耗MoBL器件横空出世。与没有ECC功能的SRAM相比,16 Mb SRAM的数据可靠性提高了几千倍,同时可延长手持式设备的电池工作时

- 关键字:

赛普拉斯 SRAM MoBL

- 使用LPC2106的Timer 1 进行的简单的中断处理。示例代码中Timer1分为FIQ和IRQ,用户可以从Flash或者SRAM中运行这些代码。示例展示了ARM构架中中断是如何操作

- 关键字:

Flash SRAM 触发中断

- RAMRAM是指通过指令可以随机的、个别的对各个存储单元进行访问的存储器,一般访问时间基本固定,而与存储单元地址无关。RAM的速度比较快,但其保

- 关键字:

SRAM DRAM SDRAM 比较

- 上世纪90年代中期,英特尔决定把SRAM整合到自己的处理器中,这给世界各地的独立式SRAM供应商带来“灭顶之灾”。最大的SRAM市场(PC 高速缓存)一

- 关键字:

可穿戴设备 物联网 SRAM

- 不同存储器都有其各自的优势和缺点,由消费类产品驱动的存储器市场在呼唤性能更优存储器技术,当然也要价格便宜。

- 关键字:

MRAM SRAM

静态随机存储器(sram)介绍

您好,目前还没有人创建词条静态随机存储器(sram)!

欢迎您创建该词条,阐述对静态随机存储器(sram)的理解,并与今后在此搜索静态随机存储器(sram)的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473