将摩尔定律推向新高度

过去50年里,影响最深远的技术成就也许就是晶体管小型化的稳步推进,它们的集成密度越来越高、功耗越来越低。自从20多年前在英特尔开始职业生涯以来,我们就一直听到这样的警告:这种无穷小的演变即将结束。然而年复一年,优秀的新型创新成果还在继续推动半导体行业进一步发展。

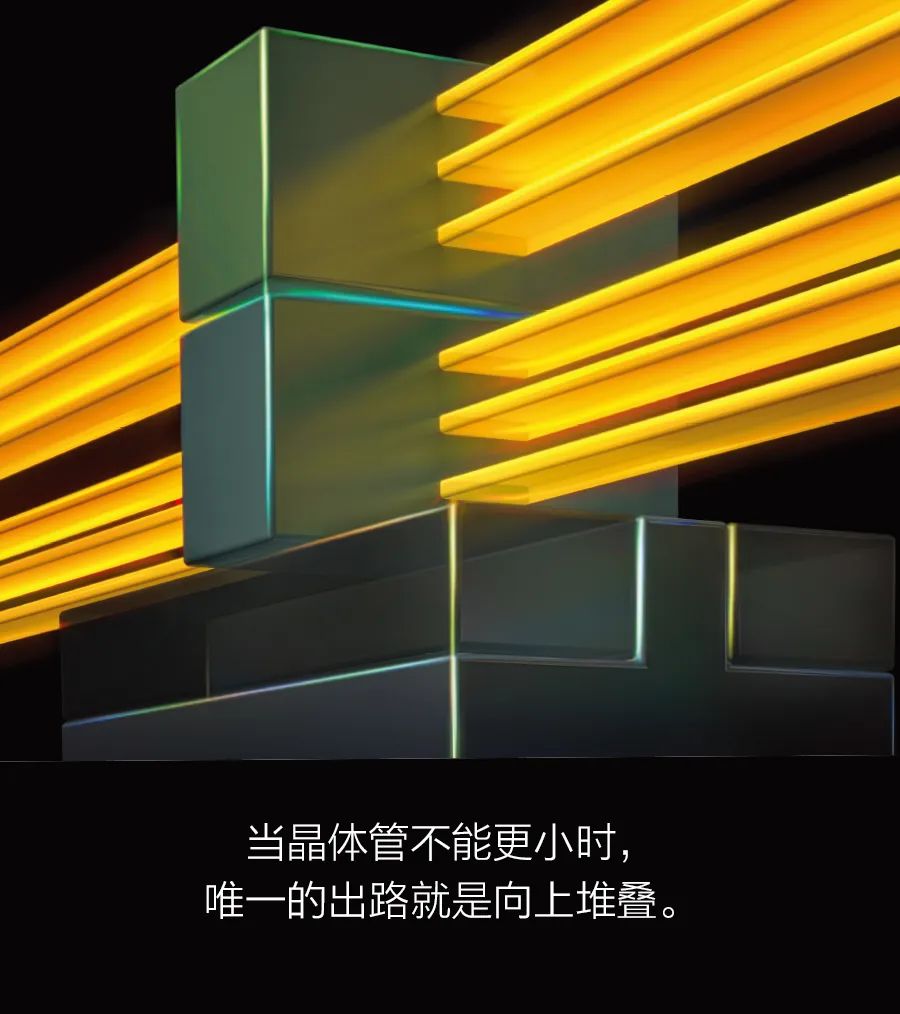

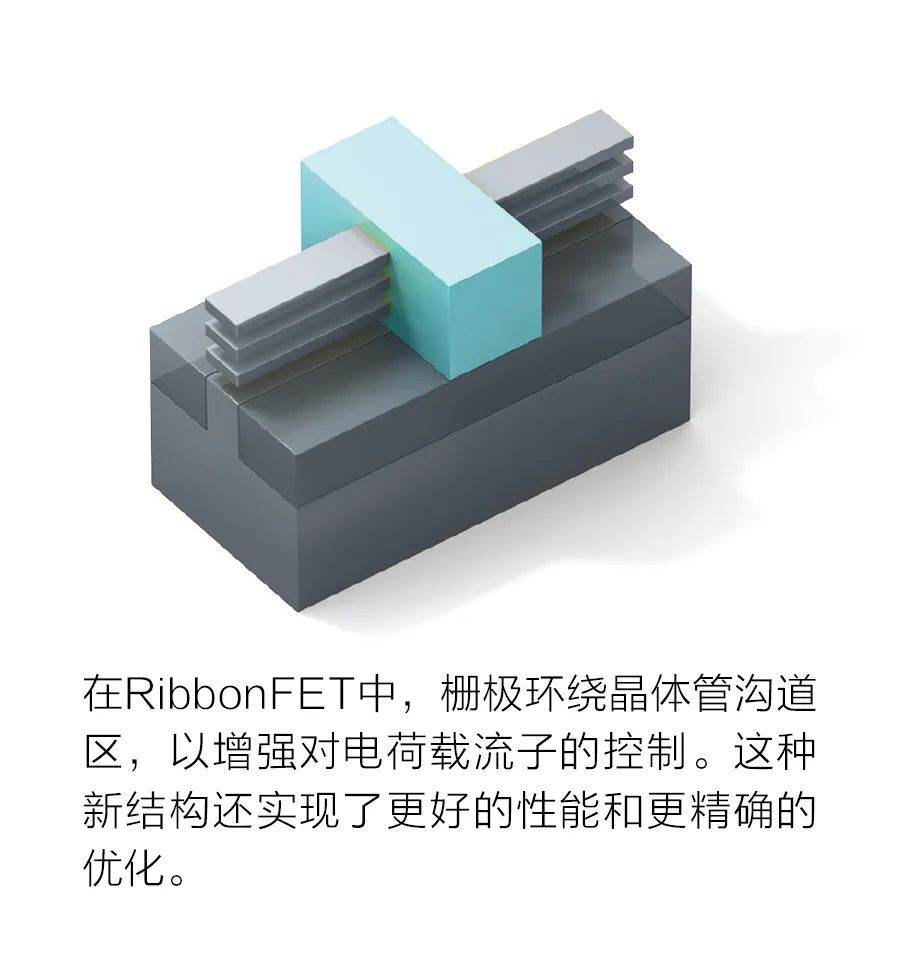

在这个过程中,我们工程师需要改变晶体管的架构,在提高性能的同时持续缩小其面积并降低功耗。带领我们走过20世纪下半叶的“平面”晶体管设计,在21世纪10年代前半期被3D鳍状器件取代。如今,随着一种新的全环绕栅极(GAA)结构即将投入生产,这些3D鳍状器件也即将被取代。但是我们必须看得更远,因为我们缩小这种新型晶体管结构(我们称之为“RibbonFET”)的能力也有限。

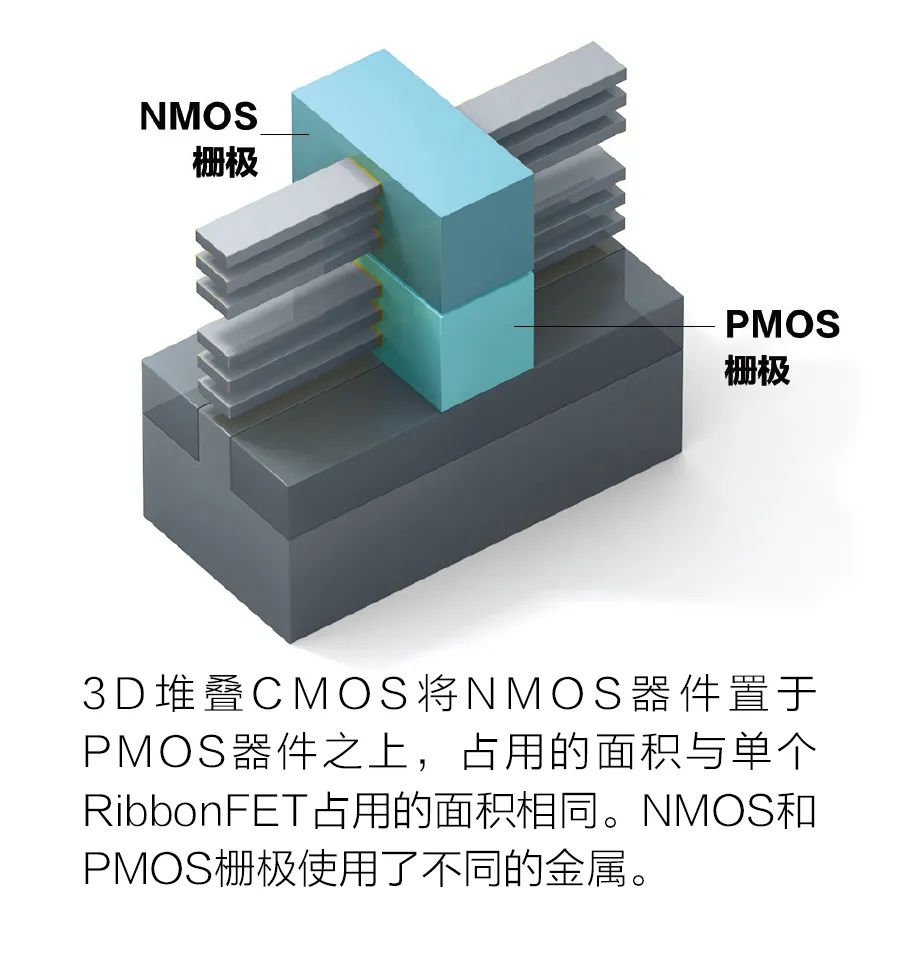

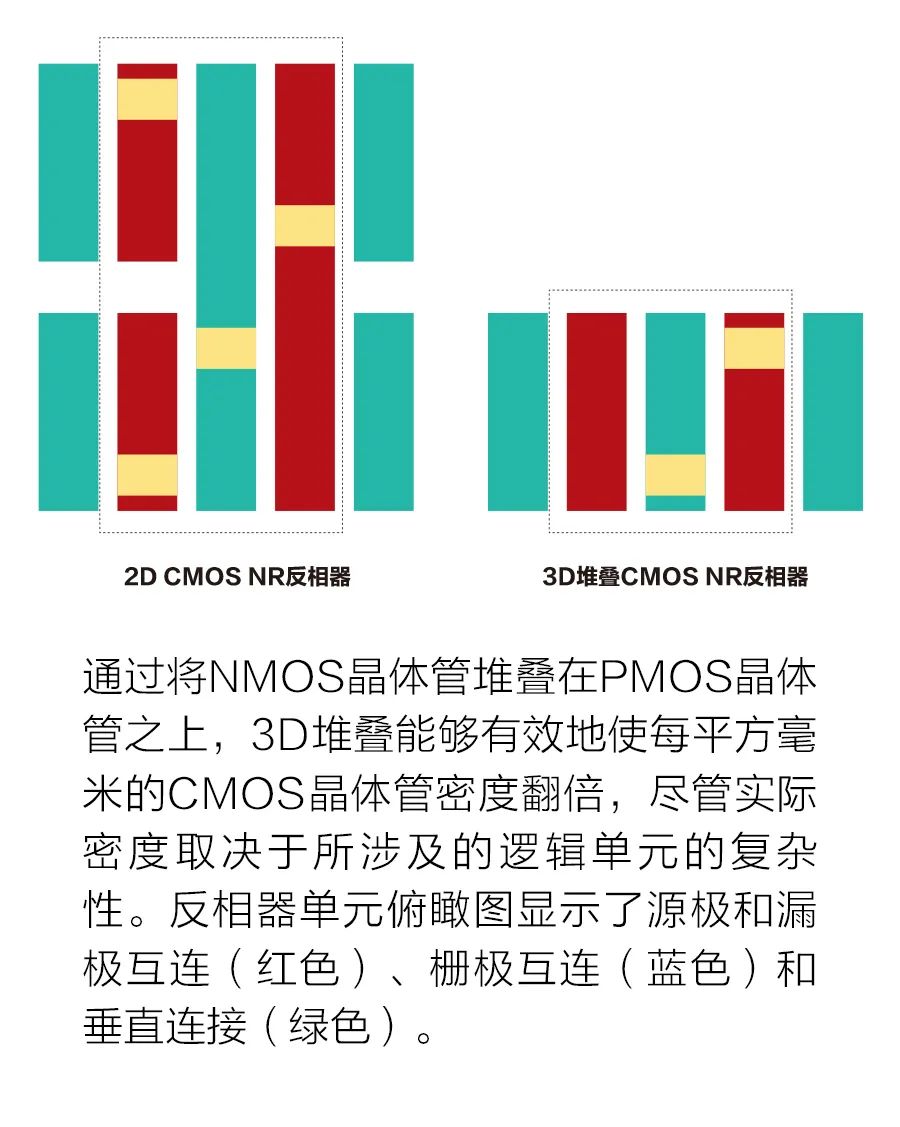

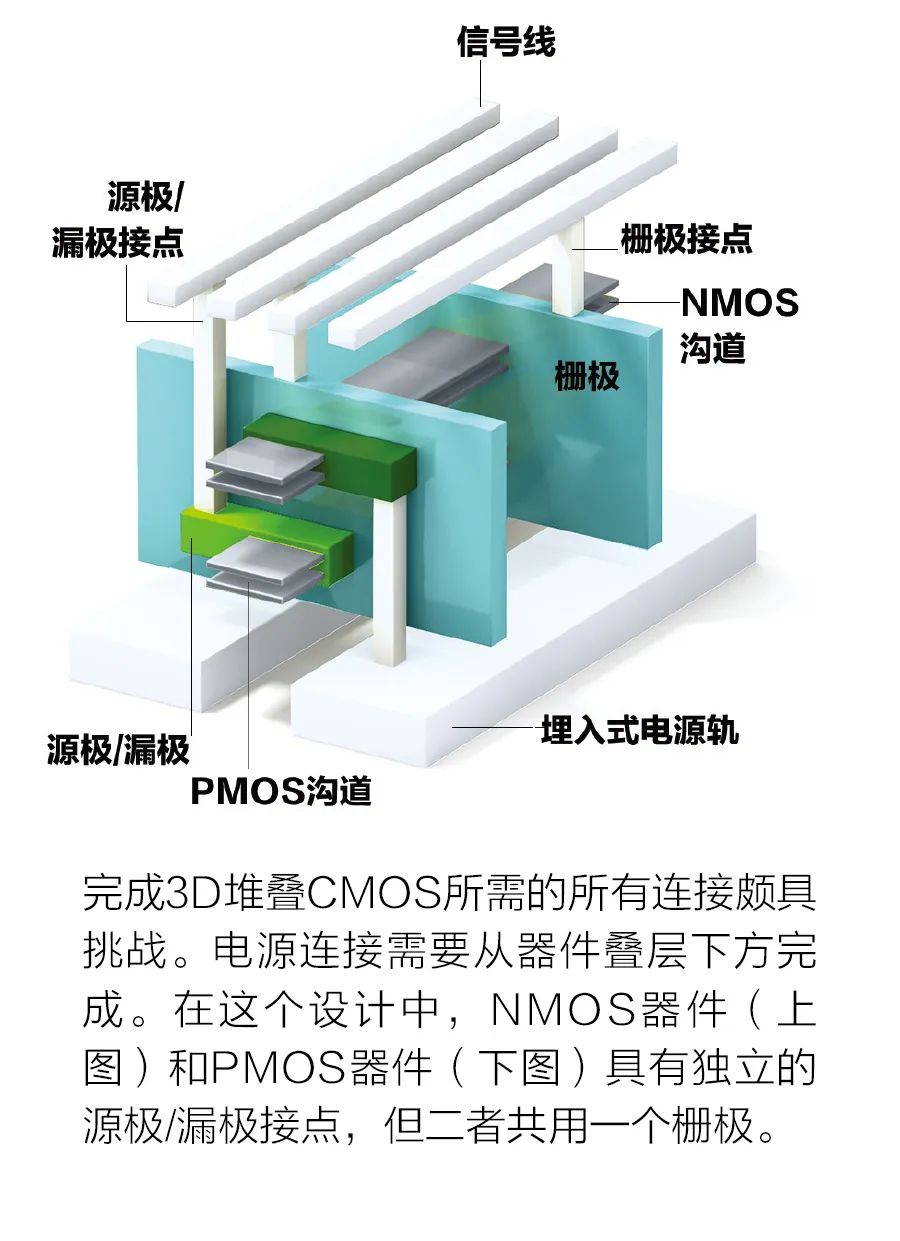

那么,未来的小型化工作要如何开展?我们将继续关注第三维度。我们开发了可以互相堆叠的实验装置,能够实现比原来小30%至50%的逻辑。至关重要的是,顶部和底部器件分属N沟道金属氧化物半导体(NMOS)和P沟道金属氧化物半导体(PMOS)两种互补类型,它们是过去几十年里所有逻辑电路的基础。我们相信这种3D堆叠的互补金属氧化物半导体(CMOS)和互补场效应晶体管(CFET)将是摩尔定律延续到下一个10年的关键。

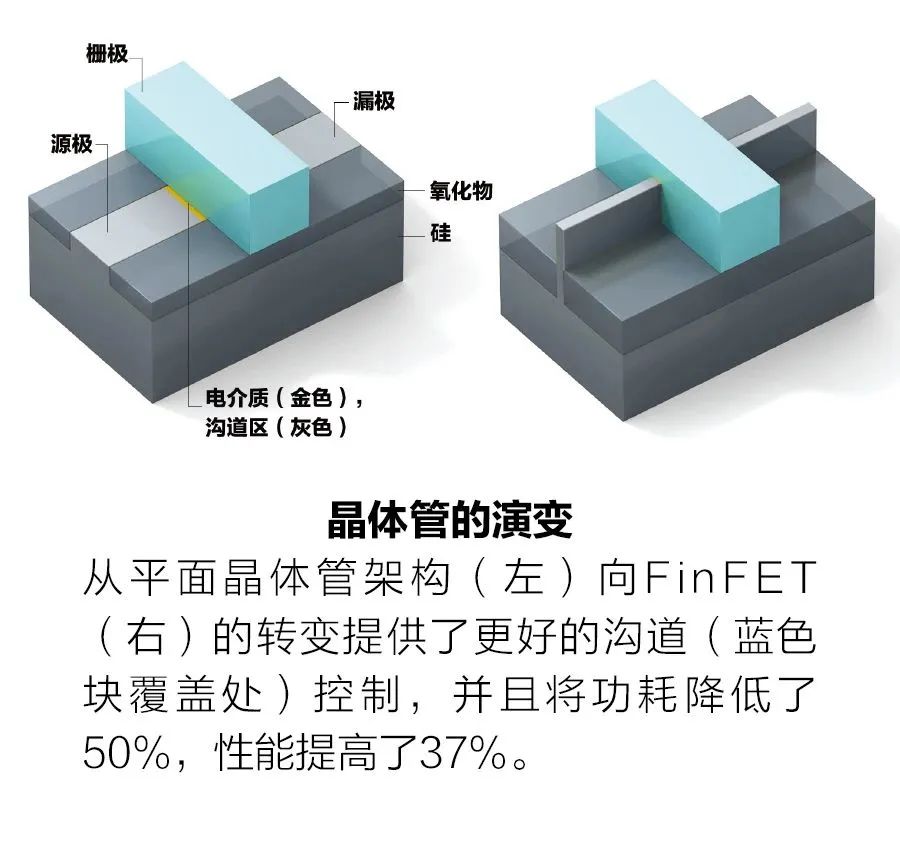

晶体管的演变

持续创新是摩尔定律的重要基础,但每一项改进都伴随着权衡取舍。要理解这些权衡以及它们为什么必然将我们引向3D堆叠CMOS,我们需要了解一点晶体管运行的背景知识。 每种金属氧化物半导体场效应晶体管(MOSFET)都有一套相同的基本部件:栅极叠层、沟道区、源极和漏极。源极和漏极经过化学掺杂后会富含移动电子(n型)或者缺乏移动电子(p型)。沟道区的掺杂情况则与源极和漏极相反。在2011年之前的先进微处理器所使用的平面晶体管中,MOSFET的栅极叠层位于沟道区正上方,目的是将电场投射到沟道区中。向栅极施加足够大的电压(相对于源极)会在沟道区产生一层移动电荷载流子,从而允许电流在源极和漏极之间流动。随着传统平面晶体管的尺寸缩小,器件物理学家称为短沟道效应的器件占据了中心位置。总的来说,由于源极和漏极之间的距离变得非常小,电流会在不应该泄漏的时候漏过沟道,因为栅电极会千方百计耗尽沟道中的电荷载流子。为了解决这个问题,业界转向了一种完全不同的晶体管架构:鳍式场效应晶体管(FinFET)。它从三面将栅极包裹在沟道周围,以实现更好的静电控制。

每种金属氧化物半导体场效应晶体管(MOSFET)都有一套相同的基本部件:栅极叠层、沟道区、源极和漏极。源极和漏极经过化学掺杂后会富含移动电子(n型)或者缺乏移动电子(p型)。沟道区的掺杂情况则与源极和漏极相反。在2011年之前的先进微处理器所使用的平面晶体管中,MOSFET的栅极叠层位于沟道区正上方,目的是将电场投射到沟道区中。向栅极施加足够大的电压(相对于源极)会在沟道区产生一层移动电荷载流子,从而允许电流在源极和漏极之间流动。随着传统平面晶体管的尺寸缩小,器件物理学家称为短沟道效应的器件占据了中心位置。总的来说,由于源极和漏极之间的距离变得非常小,电流会在不应该泄漏的时候漏过沟道,因为栅电极会千方百计耗尽沟道中的电荷载流子。为了解决这个问题,业界转向了一种完全不同的晶体管架构:鳍式场效应晶体管(FinFET)。它从三面将栅极包裹在沟道周围,以实现更好的静电控制。 2011年,英特尔推出了22纳米节点的FinFET,以及第三代酷睿处理器,之后,该器件架构一直是摩尔定律的主力。有了FinFET,我们能够在更低的电压下工作并进一步减少泄露,与上一代平面架构相比,在同等性能水平下,功耗可降低约50%。FinFET的切换速度也更快,性能提高了37%。由于导电发生在“鳍”的两个垂直面上,所以与只沿一个表面导电的平面器件相比,这种器件可以驱动更多的电流通过给定面积的硅。不过,在转向FinFET时,我们也有所舍弃。在平面器件中,晶体管的宽度是由光刻定义的,因此它是一个非常灵活的参数。但在FinFET中,晶体管宽度以离散增量的形式出现,一次增加一个鳍,这种特性往往被称为“鳍量化”。FinFET虽然可能很灵活,但鳍量化仍然是一个重要的设计约束。它的设计规则和增加更多鳍片以提高性能的愿望会增加逻辑单元的总面积,而且会使将单个晶体管变成完整逻辑电路的互连堆叠变得更加复杂。这也增大了晶体管的电容,从而降低了其切换速度。因此,虽然FinFET作为行业的主力为我们提供了很好的服务,但我们仍然需要一种更加完善的新方法。正是这种方法将我们引向了下面即将介绍的3D晶体管。

2011年,英特尔推出了22纳米节点的FinFET,以及第三代酷睿处理器,之后,该器件架构一直是摩尔定律的主力。有了FinFET,我们能够在更低的电压下工作并进一步减少泄露,与上一代平面架构相比,在同等性能水平下,功耗可降低约50%。FinFET的切换速度也更快,性能提高了37%。由于导电发生在“鳍”的两个垂直面上,所以与只沿一个表面导电的平面器件相比,这种器件可以驱动更多的电流通过给定面积的硅。不过,在转向FinFET时,我们也有所舍弃。在平面器件中,晶体管的宽度是由光刻定义的,因此它是一个非常灵活的参数。但在FinFET中,晶体管宽度以离散增量的形式出现,一次增加一个鳍,这种特性往往被称为“鳍量化”。FinFET虽然可能很灵活,但鳍量化仍然是一个重要的设计约束。它的设计规则和增加更多鳍片以提高性能的愿望会增加逻辑单元的总面积,而且会使将单个晶体管变成完整逻辑电路的互连堆叠变得更加复杂。这也增大了晶体管的电容,从而降低了其切换速度。因此,虽然FinFET作为行业的主力为我们提供了很好的服务,但我们仍然需要一种更加完善的新方法。正是这种方法将我们引向了下面即将介绍的3D晶体管。

堆叠CMOS

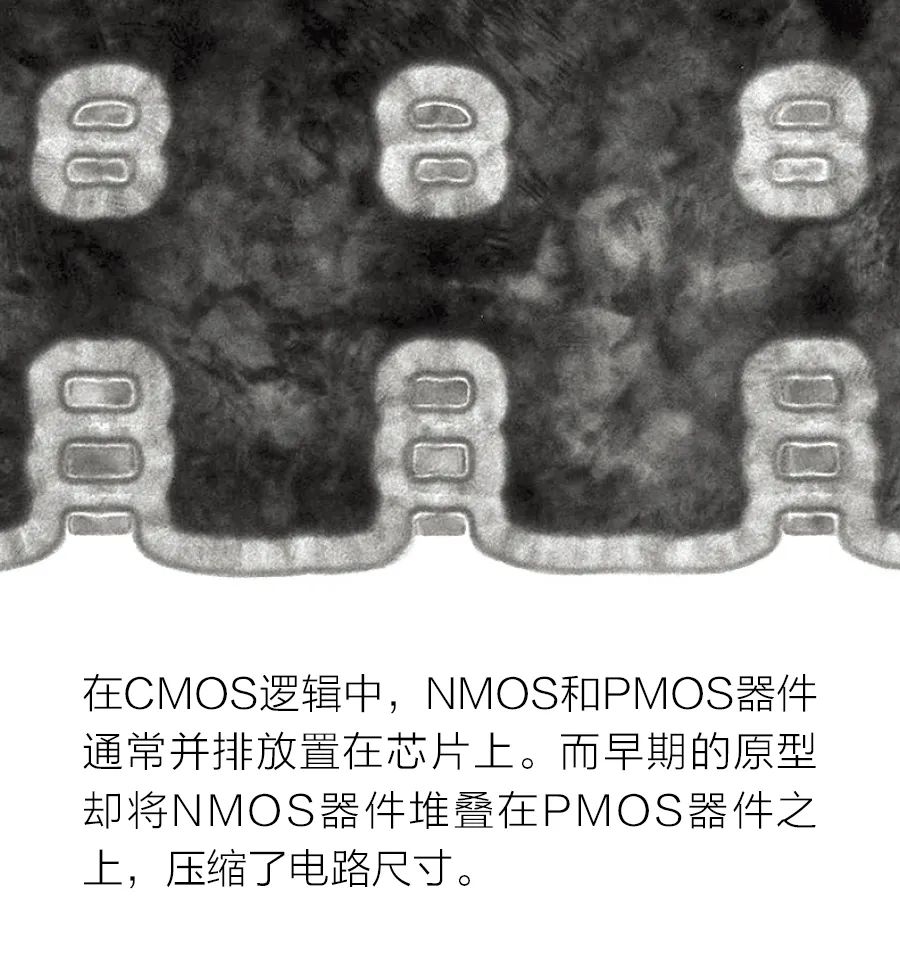

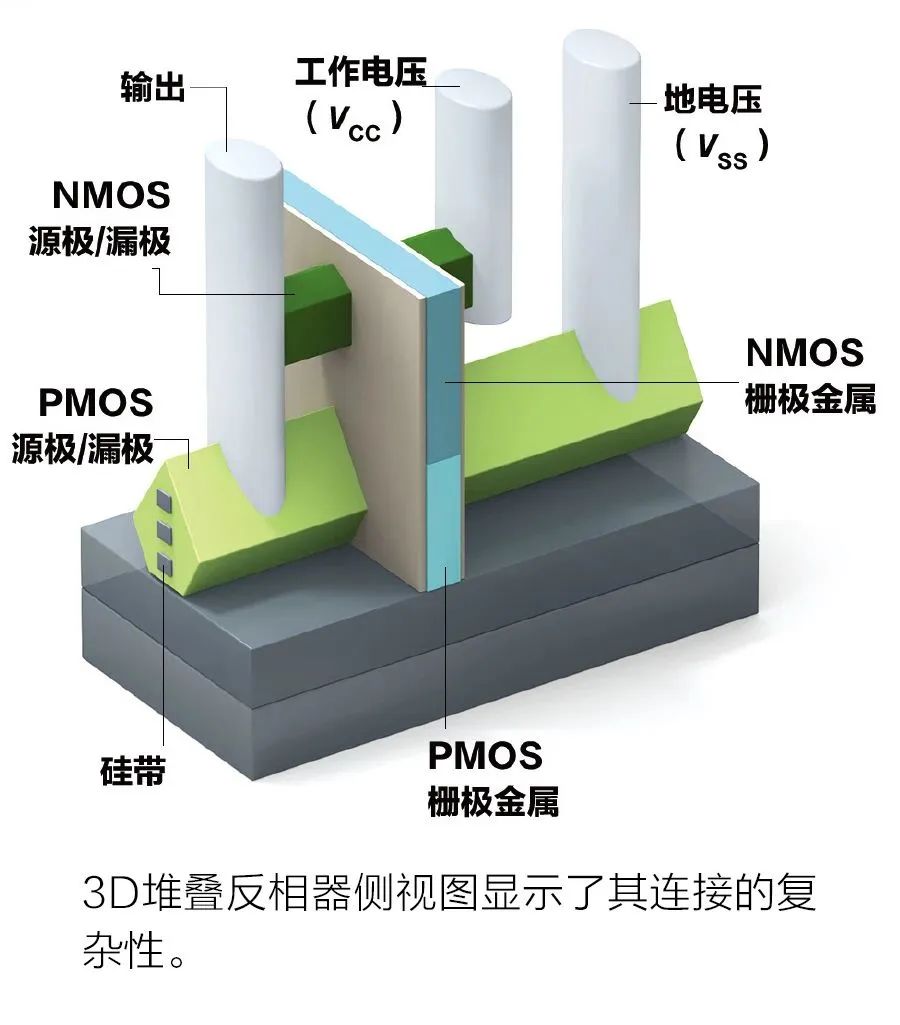

平面晶体管、FinFET和RibbonFET有一个共同点,即它们都采用了CMOS技术,如前所述,CMOS技术由n型(NMOS)和p型(PMOS)晶体管组成。20世纪80年代,CMOS逻辑成为了主流,因为它消耗的电流比替代技术(尤其是纯NMOS电路)少得多。更少的电流能够实现更高的工作频率和更高的晶体管密度。到目前为止,所有CMOS技术都是将标准NMOS和PMOS晶体管对并排放置。但在2019年IEEE国际电子设备会议(IEDM)的专题演讲中,我们介绍了3D堆叠晶体管的概念,它将NMOS晶体管置于PMOS晶体管之上。次年,在2020年IEEE国际电子设备会议上,我们展示了第一个采用这种3D技术的逻辑电路设计,它是一款反相器。结合适当的互连,3D堆叠CMOS方法有效地将反相器的尺寸减半、面积密度加倍,并进一步推高了摩尔定律的极限。

摩尔定律的未来

有了RibbonFET和3D CMOS,我们就有了一条将摩尔定律延续至2024年以后的清晰道路。在2005年的一次采访中,戈登•摩尔在被问及他的定律会变成什么样时表示:“我不时惊讶于我们取得进展的能力。一路走来,有好几次我都以为已经走到了尽头,会逐渐停止,但我们具有创造力的工程师却想出了解决办法。”随着向FinFET的转变和接踵而来的优化、目前RibbonFET的发展和最终3D堆叠CMOS的发展,以及无数与之相关的封装改进,我们认为摩尔先生将再次感到惊讶。作者:Marko Radosavljevic、Jack Kavalieros

免责声明:本文版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请第一时间告知,我们将根据您提供的证明材料确认版权并按国家标准支付稿酬或立即删除内容!本文内容为原作者观点,并不代表本公众号赞同其观点和对其真实性负责。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。