3D DRAM,Chiplet芯片微缩化的“续命良药”

来源:ASPENCORE

在边缘计算领域里,对DRAM带宽的要求远高于容量,此时采用Chiplet方式集成3D DRAM存储方案,就可以同时提供高带宽和低功耗。

今年2月,在正式加入UCIe™(Universal Chiplet Interconnect Express™)产业联盟之后,华邦电子随即宣布其创新产品CUBE: 3D TSV DRAM和3DCaaS(3D CUBE as a Service)一站式服务平台,将成为公司向客户提供优质定制化内存的首选解决方案。

芯片微缩化的“续命良药”CUBE是Customized/Compact Ultra Bandwidth Elements,即“半定制化紧凑型超高带宽DRAM”的简称。华邦电子次世代内存产品营销企划经理曾一峻在向《电子工程专辑》说明CUBE核心价值时表示,新能源汽车、5G、可穿戴设备等领域的不断发展,对芯片性能的需求越来越高,但如果采用诸如“直接在5nm SoC裸片上堆叠7nm SRAM裸片”的做法,会因为带入太多TSV工艺架构而导致芯片成本暴涨。

于是,采用先进封装技术的Chiplet成为了芯片微缩化进程的“续命良药”。“这也是华邦解决方案的思路”,按照曾一峻的解释,在边缘计算领域,华邦将SoC裸片置上,DRAM裸片置下,省去了SoC中的TSV工艺(图中虚线部分所示),从而大幅降低了SoC裸片的尺寸与成本。与此同时,3D DRAM TSV工艺又可以将SoC信号引至外部,使它们成为同一颗芯片,进一步缩减了封装尺寸。

另一方面,考虑到现在的AI芯片都有着很高的算力需求,SoC裸片置上也可以带来更好的散热效果。因此,华邦方面认为,按照这样的方式进行CUBE 3D DRAM 裸片堆叠可以带来高带宽、低功耗和优秀的散热表现,这也是华邦CUBE解决方案主要面向低功耗、高带宽、中低容量内存需求应用的主要原因。

众所周知,DRAM裸片中都会包含电容,华邦CUBE芯片也不例外。目前,先进制程SoC芯片的核心电压约为0.75V-1V,运行过程中电源产生的波动会影响功耗和信号稳定性。但CUBE芯片所采用的硅电容(Si-Cap)却可以有效降低电源波动带来的影响。

下图是华邦当前硅电容规格和制程的进展。可以看到,尽管电容缩小到了原来的一半,但是运行的经时击穿电压(TDDB)却被提高了1倍至1.5V(这也是目前大部分先进制程芯片的核心电压),击穿电压也是目前先进制程所需的5V,因此1500nF/(mm2)是完全符合目前先进制程芯片的电容需求。而根据规划,下半年还会有更优规格的硅电容产品面世。

再来关注一下华邦DRAM堆叠和中介层(Interposer)架构的演进。如图所示,由于中介层也是华邦提供,因此客户可以得到一个包括DRAM、中介层、硅电容在内的整体解决方案,这也是华邦加入UCIe后做出的贡献之一。

另一个值得关注的优势来自功耗的降低。由于SoC裸片和DRAM裸片堆叠的时候,相比于传统的引线键合(Wire Bonding),微键合(Micro Bonding)工艺可以将1000微米的线长缩短至40微米,仅有传统长度的2.5%,在未来的混合键合(Hybrid Bonding)封装工艺下,线长甚至可以缩短至1微米。这意味着在芯片内部,信号所经过的传输距离更短,功耗自然也得到相应的降低。此外,当采用混合键合工艺时,两颗堆叠的芯片其实可以被看作同一颗芯片,因此内部传输信号和SIP表现会更优秀。

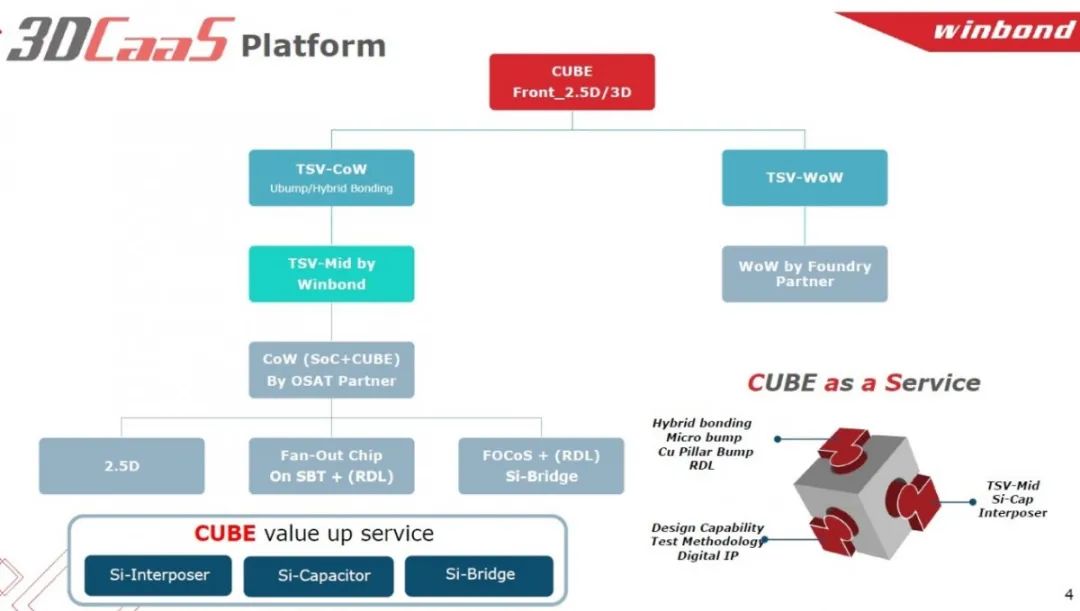

与CUBE同时出现的还包括3D CaaS平台,也就是 CUBE as a Service。这意味着对于客户来说,华邦不仅仅提供3D TSV DRAM KGD内存芯片和针对多芯片设备优化的2.5D/3D后段工艺(采用CoW/WoW),还可获取由华邦的平台合作伙伴提供的技术咨询服务,是一套完整且全面的CUBE产品支持,并享受Silicon-Cap、interposer等技术的附加服务。

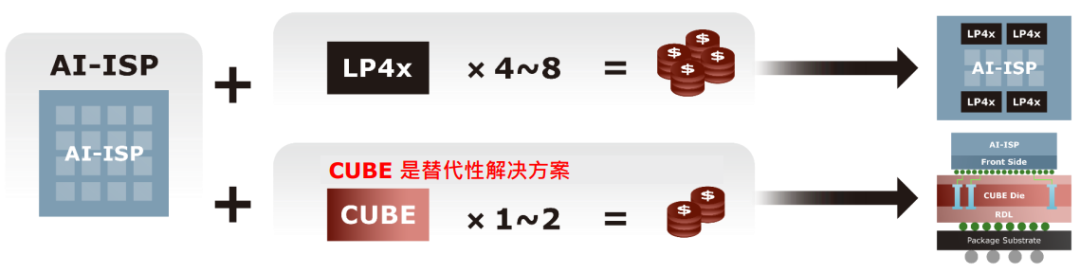

ChatGPT的面世带动了AI应用领域的再次火热,而CUBE就可以应用到AI-ISP架构中。

上图中的灰色部分代表AI-ISP中的神经网络处理器(NPU),如果AI-ISP要实现大算力,就需要很大的带宽,或者是SPRAM加持。但目前来看,在AI-ISP上使用SPRAM成本高昂,转而使用LPDDR4则需要4-8颗,如果用到传输速度为4266Mhz的高速LPDDR4,还需要依赖7nm或12nm的先进制程工艺。

相比之下,CUBE解决方案就可以允许客户使用成熟制程(28nm/22nm)获得类似的高速带宽。简单而言,CUBE芯片可以通过多个I/O(256或者512个)结合28nm SoC提供500MHz运行频率,以及最高256GB/s带宽。据透露,华邦在未来可能会和客户共同探讨64GB/s带宽的合作可能性,如果成功,I/O数量和裸片尺寸都将进一步缩小。

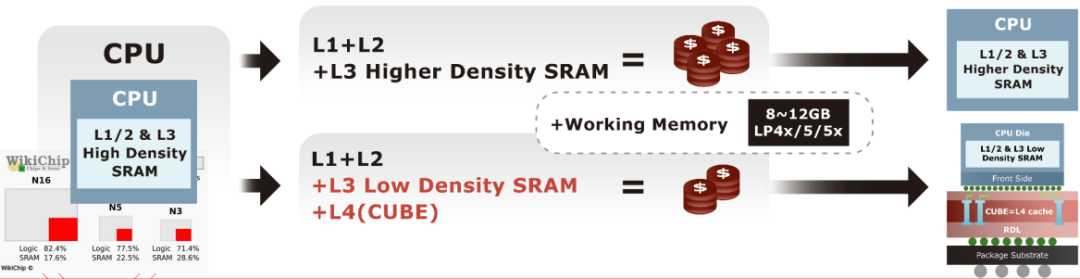

在下面的应用场景中,CPU的高速运算需求对制程的要求从16nm、7nm、5nm到3nm,越来越高。但不难发现,尽管制程工艺越来越先进,图中红色部分所代表的SRAM占比并没有同比例缩小,因此当需要实现AI运算或者高速运算的情况下,就需要将L3缓存SRAM容量加大,即便采用堆叠方式达到几百MB,也会导致高昂的成本。

华邦的做法是将L3缓存缩小,转而使用L4缓存的CUBE解决方案。这并不意味着CUBE解决方案的时钟传播延迟(Latency)等同于SRAM,而是可以作为L4缓存。原因在于CUBE可以进行定制化的设计,使得时钟传播延迟比一般的DRAM还要短。同时,考虑到AI模型在某些情况下需要外置一定容量的内存,例如在某些边缘计算场景下会需要8-12GB LPDDR4/LPDDR5,因此在需要的情况下,也可以外挂高容量工作内存(Working Memory)。

“在边缘计算领域里,对DRAM带宽的要求远高于容量,此时采用Chiplet方式集成类似CUBE的存储方案,就可以同时提供高带宽和低功耗。”但曾一峻也同时强调称,毕竟Chiplet芯片需要兼容多个接口协议才能避免造成信号偏差,因此,如何进一步缩小3D DRAM的裸片尺寸,如何更好的实现不同芯粒间的互联互通,是绕不开的挑战。

华邦DRAM技术路线图相对于市场上三大头部内存厂商而言,华邦主要专注于利基型内存,产品容量一般最大为8GB,其特点是不需要非常先进的制程,并以KGD为主,便于与SoC进行合封。

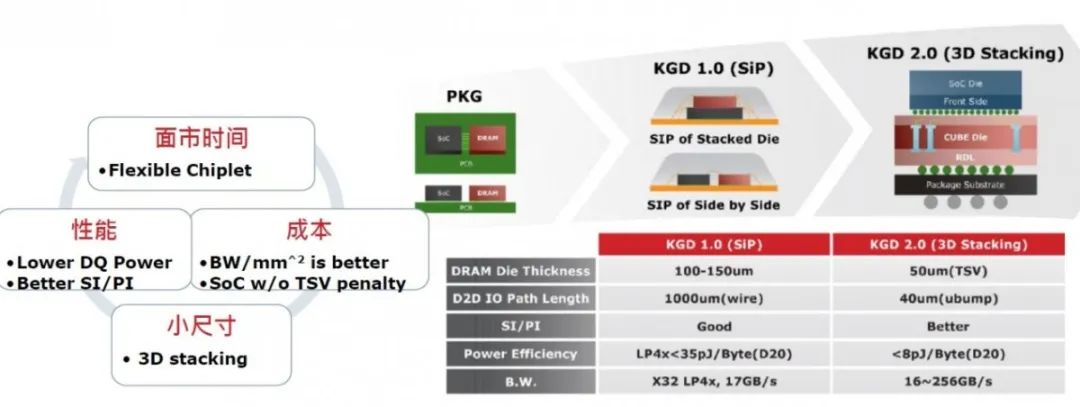

在KGD 1.0(SiP)中,DRAM Die厚度约为100-150微米,裸片至裸片(Die to Die)的I/O路径为1000微米,目前这种性能的KGD信号完整性/电源完整性(SI/PI)是主流的,也是够用的。华邦方面曾经对LPDDR4的电源效率进行过估算,其小于35pJ/Byte,带宽方面X32 LPDDR4x每I/O为17GB/s。

当进化到KGD 2.0(3D堆叠)后,得益于TSV的深宽比能力,DRAM Die厚度可以达到50微米的深度,未来,通过Hybrid Bonding工艺还可以实现1微米的距离。同时,信号完整性/电源完整性(SI/PI)性能更好,功耗更低,可以达到甚至低于LPDDR4的四分之一(为8pJ/Byte),而带宽可以实现16-256GB/s。

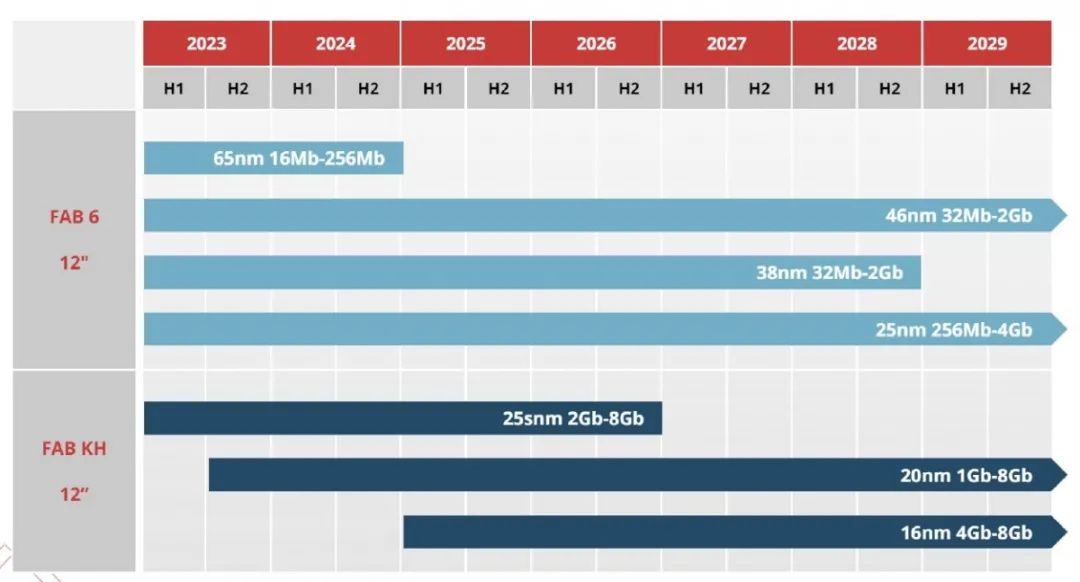

目前,华邦拥有两座12寸晶圆厂,一座是位于台中的Fab 6工厂,另一座是在高雄新建的第二座工厂,其产能为1万片/月左右,后续将逐渐提升至1.4万片-2万片/月。

从制程工艺角度来看,高雄工厂投产后,华邦会将一些先进制程的DRAM产能转移至高雄厂,台中厂的中小容量DRAM制程会维持在65nm、46nm、38nm和25nm,且无意再向更小制程演进,而是专注于成熟制程产品。高雄厂已经量产的包括25nm 2GB和4GB两种产品,20nm产品预计在今年年中进入量产阶段,并继续向19nm制程演进。

华邦电子大陆区产品营销处处长朱迪再次强调了华邦对于DDR3的生产和支持。尽管他认为像三星这样的大厂逐渐舍弃DDR3和中小容量DDR4是一个大概率的事件,但从实际使用情况来看,4Gb DDR3产品将有望继续被广泛采用至少到2027-2028年,尤其在工业和汽车领域需要长期支持。而且,相同容量相同速度下,DDR3较DDR4更具成本效益(相同制程下,与DDR3相比,Die尺寸DDR4增加10%,LPDDR4增加18%),DDR4将会持续向更高容量发展,并随着PC和服务器市场的需求迁移至DDR5。

根据规划,DDR3仍将保持1Gb、2Gb、4Gb和8Gb四种容量,并计划在2025年演进至16nm;DDR4方面,当20nm制程就绪之后,高雄厂会在2024年初量产DDR4 DRAM芯片。

“利基型存储市场大约只占整个存储市场的10%,它的供需相对而言是比较平衡和稳定的。在当前终端客户、代理商、以及原厂库存都比较低的情况下,确实有可能会出现缺货的情况,但对具体时间节点做出判断为时尚早,需要做进一步的观察。”朱迪说。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。