继不久前对外公开展示了面向2nm以下尖端制程制造的High NA EUV光刻机之后,近日,AMSL在其2023年度报告当中还披露了其未来更为先进的Hyper-NA EUV技术的进展,并预计Hyper-NA EUV光刻机可能将会在2030年之际开始商用,为未来更尖端的芯片生产技术提供助力。

继不久前对外公开展示了面向2nm以下尖端制程制造的High NA EUV光刻机之后,近日,AMSL在其2023年度报告当中还披露了其未来更为先进的Hyper-NA EUV技术的进展,并预计Hyper-NA EUV光刻机可能将会在2030年之际开始商用,为未来更尖端的芯片生产技术提供助力。

ASML目前的EUV工具的数值孔径(NA)为0.33,可实现13.5nm左右的分辨率,透过单次曝光,可以产生26nm的最小金属间距和25-30nm尖端到尖端的近似互连空间间距,这些尺寸足以满足4/5nm节点制程的生产需求。尽管如此,业界仍然需要更小的21-24nm间距的3nm制程工艺,这就是为什么台积电的N3B制程技术被设计为使用标准EUV双图案化技术来实现更小的间距,但这种方法将会相当昂贵。

目前ASML已经开始交付的首款High NA EUV系统(EXE:5000)数值孔径已经由传统EUV的0.33提升到了0.55,分辨率也由13.5nm提升到了8nm,可以实现16nm的最小金属间距,对于2nm以下制程节点将非常有用。根据Imec的预计,这即使对于1nm节点技术,High NA EUV系统也能提供解决方案。另外,在生产效率方面,High NA EUV系统每小时可光刻超过 185 个晶圆,与已在大批量制造中使用的 EUV 系统相比还有所增加。ASML还制定了到 2025 年将新一代High NA EUV系统(EXE:5200)的生产效率提高到每小时 220 片晶圆的路线图。

未来,随着制程工艺的继续推进,当进入1nm制程工艺节点之后,晶体管的金属间距将需要变得更小,届时晶圆制造商将需要比High NA EUV光刻机更复杂的工具,这也是ASML为何计划开发出具有更高数值孔径Hyper NA EUV光刻机的原因。

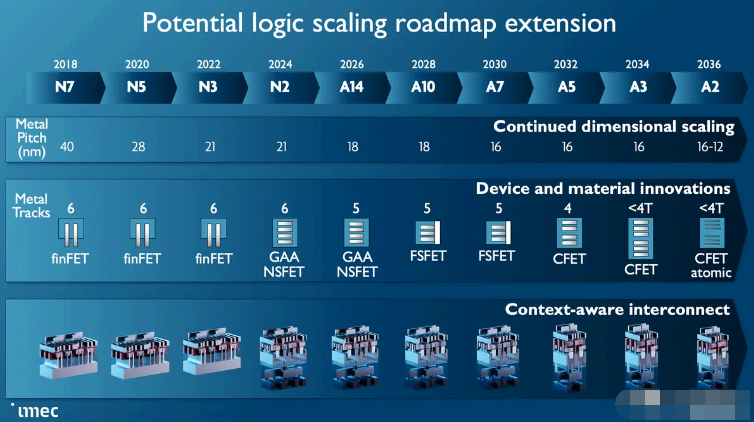

△根据此前imec的预计,凭借晶体管技术以及先进的制造工具的出现,2030年将进入7埃米(0.7nm)时代,2032年将有望进化到5埃米(0.5nm),2036年将有望实现2埃米(0.2nm)。

在2022年之时,Martin就曾指出,ASML正在研究Hyper NA技术的可行性。不过,当时ASML尚未做出最终决定。当时ASML担忧的是Hyper NA技术的制造成本增长速度和目前High-NA EUV技术一样,那么高昂的成为将会使得Hyper NA EUV光刻机在经济层面几乎不可行。

要知道目前全球仅剩下了台积电、三星、英特尔这三家尖端逻辑制程芯片制造商,虽然日本的Rapidus可能会发展成为新的玩家,但即便如此,这个领域的玩家已经是非常的少了。

根据资料显示,ASML标准数值孔径的EUV光刻机(NXE系列)目前售价约为1.83亿美元,而High NA EUV光刻机(EXE:5000)的售价约为3.8亿美元,增长了一倍多,如果Hyper NA EUV光刻机成本也将继续增长一倍,一台价格就将超过7.6亿美元,这样的价格即便是台积电、三星、英特尔这样的巨头恐怕也难以承受。

不过,从ASML 2023年年度报告中披露的信息来看,ASML似乎已经解决了Hyper NA EUV的成本和交付周期问题。

ASML首席技术官Martin van den Brink在ASML 2023年年度报告中表示,NA值高于0.7的Hyper NA光刻机无疑是继续发展芯片生产技术的机会,预计将从2030年左右开始获得应用。Hyper-NA光刻可能与逻辑制程芯片更相关,并且将提供比High NA EUV光刻双重图案化更实惠的解决方案,同时对于DRAM制程来说也是一个机会。

“对我们来说,关键是Hyper NA正在推动我们的整体EUV平台能力,进一步优化了成本和交付周期。就整个行业而言,数字化将继续推动许多正在改变我们的解决方案。尽管像我们的EUV平台这样的系统需要大量的能源,但我认为,我们通过开发智能电网和电动汽车等技术,为减少温室气体排放做出了积极贡献。未来,更多这样的技术将随之而来。”Martin说道。

编辑:芯智讯-浪客剑