使用EYEQ特性实现高速串行IO的最佳相位接收判决

—— Using EYEQ Characteristics to Realing Best Phase Receiver Sentence of High-Speed Serial IO

现有的很多高速串口协议,都要求很低的误码率,比如CEI-6G-LR(6.375G, 40英寸走线)就要求1E-15的误码率。为满足此类低误码率要求,ALTERA高端的FPGA STRATIX IV系列,提供了片上信号质量检测电路(EYEQ),帮助客户在高速串行IO接收处找到最优的采样位置。

本文引用地址:http://www.amcfsurvey.com/article/116959.htm通常眼图的张开度是用来衡量接收端信号的质量。片上信号质量检测电路(EYEQ)就是一个调试诊断工具来帮助分析接收的数据路径,包括接收端的增益,噪声水平。

原理

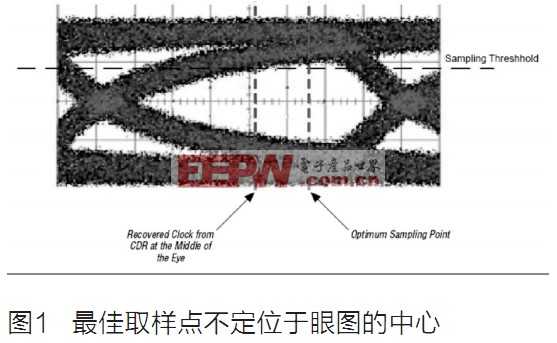

缺省情况下,CDR恢复时钟是在眼图的中间位置采数据,如图1的红色虚线位置,但是根据这个眼图的张开程度,最佳采样位置应该是在绿色虚线部分。只有在绿色虚线位置,眼高最大,这样采样到的数据才具有最低的误码率。

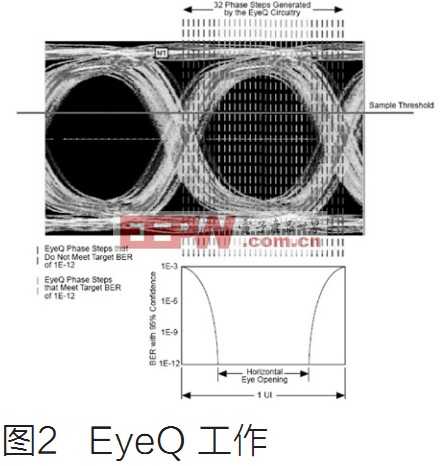

EYEQ电路在一个完整的信号周期(UI)中,将采样时钟放到32个相位上,用户可以根据每个不同相位时的误码率,找出最佳采样相位。如图2所示。

评论