软件数字收音机系统,包括原理图、电路图及源代码

摘要: 本系统采用430单片机,FPGA。通过天线收到不同频率的电磁波,通过单片机控制本振频率的产生,从而选定不同频率的电台,经过混频得到的信号由FPGA解调,最后通过功放由喇叭放出声音。本系统在设计中注意低功耗处理和力求高性价比等细节。

本设计主要特点:

1. MB1504控制产生本振,具有高效,稳定,简单特点。

2.FPGA稳定性好,处理速度快。

3. 数字式收音机接收数据更精确,收到的电台更多更精确。

1.方案设计与论证

1.1主控系统选择

方案一:采用高性能嵌入式系统,比如ARM。如果采用此方案,可以很好的解决数据处理和控制功能,但是ARM价格昂贵且本科阶段很少接触,在短时间内完成困难比较大。

方案二:采用一般单片机,如51单片机。但是51单片机内部资源不够,很多功能无法实现。

方案三:采用430高性能单片机来实现,用来处理控制本振频率。

考虑到方案的可实行性和性价比,我们采用M430F1611单片机,此款单片机可实现高速运算,存储空间大,价格低廉,性价比极高。

1.2本振选择

方案一:选择分立元件搭配出,但是此方法难度太高,并且误差干扰都很大。

方案二:完全选择专用芯片有单片机控制。此方法简单,但价格昂贵。

方案三:使用数字锁相环 芯片和分立元件组合的vco电路。

芯片和分立元件组合的vco电路。

考虑到价格,工作频率以及灵敏度等因素。本系统采用MB1504 锁相环 芯片和分立元件搭VCO。

芯片和分立元件搭VCO。

1.3变频选择

方案一:采用一次变频。此种方法方案简单,容易实现,但对后端AD要求较高。

方案二:采用多次变频。整体设计更加复杂,误差也将各大,实现有难度。

考虑到收音机对数据要求较高,和整体性能。本系统采用一次变频,芯片使用NE602。

1.4数据处理模块选择

方案一:采用专用解调芯片,此方法方案简单,但扩展和开发性都很差。

方案二:采用FPGA芯片解调,此方案结构清楚简单,稳定性好,但价格昂贵。

本系统选用了FPGA芯片作为解调,确保系统的开发性和准确性。

1.5音频处理

方案一: 使用三极管进行放大,效果不好并且复杂。

方案二: 使用专用功放芯片。

综合考虑,本系统选用功放芯片LM386。

小结:

经过几番仔细的论证和比较,我们决定了本系统主要模块方案如下:

音频处理方案:LM386。

主控制器:MSP430单片机。

本振电路方案:MB1504+分立元件的VCO。

变频模块:NE602。

数据处理模块:FPGA最小系统板。

2.电路设计

2.1系统组成原理

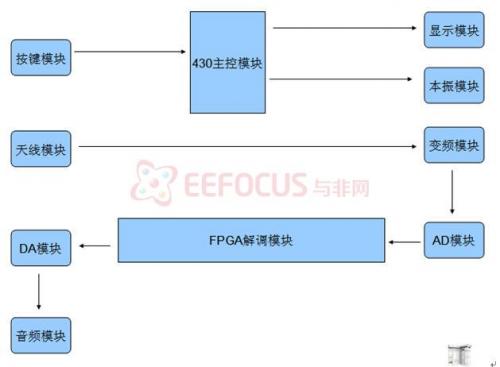

本系统由本振模块,变频模块,主控单片机,FPGA解调模块,音频模块,AD模块,DA模块等组成。

图2.1系统组成原理图

2.2本振电路

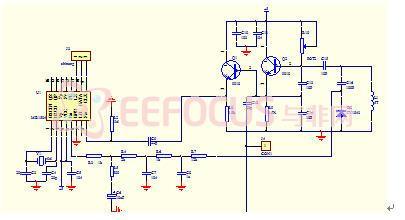

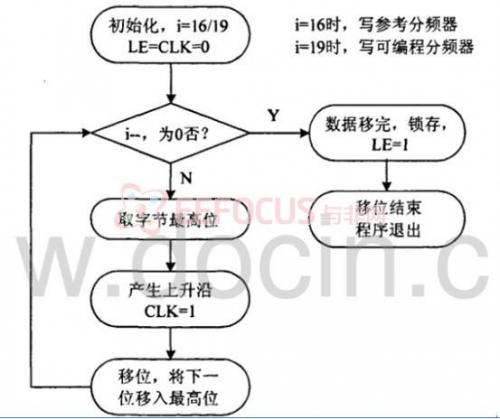

通过单片机控制MB1504锁相环 和压控振荡器产生所需要的频率。

和压控振荡器产生所需要的频率。

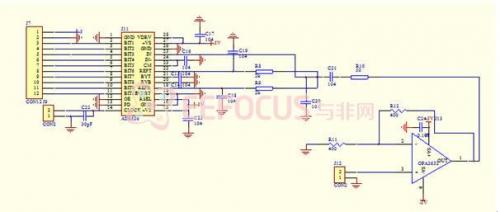

图2.2本振电路原理图

2.3变频模块

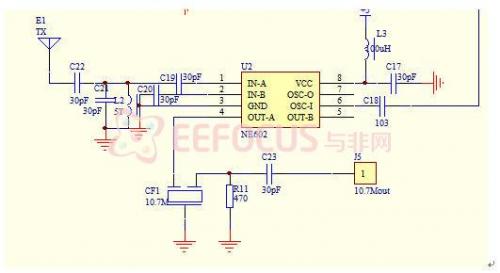

本振产生的频率与天线接收进来的频率经过NE602混频放大。

图2.3变频模块原理图

2.4AD,DA模块

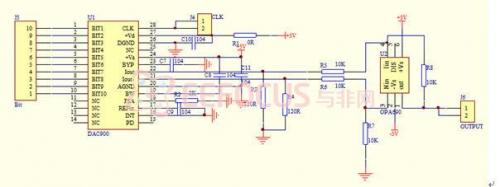

变频之后的模拟信号经过AD采入FPGA解调,解调之后再用DA转换为模拟信号

图2.4.1 DA模块

图2.4.2 AD模块

2.5声音模块

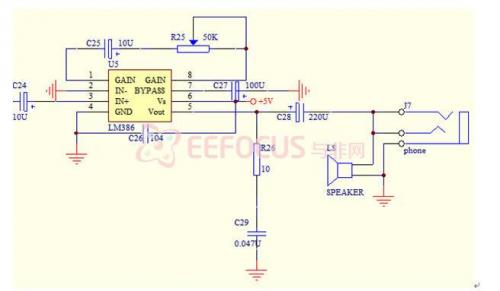

模拟信号经过功放放大后送入喇叭,还原成声音信号。

图2.5功放电路

3.软件设计

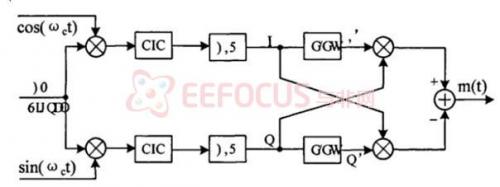

3.1FPGA解调

、

、 为正交信号,cM Signal为ADC采样到的数字cM中频数据,经过两路正交相乘后进行CIC抽取,cIo低通滤波器用来滤除正交相乘后产生的和频分量,包含语音信息中的零中频信号分量被保留。正交零中频分量再经过求导交叉相乘,求差,即为有用的语音信息。

为正交信号,cM Signal为ADC采样到的数字cM中频数据,经过两路正交相乘后进行CIC抽取,cIo低通滤波器用来滤除正交相乘后产生的和频分量,包含语音信息中的零中频信号分量被保留。正交零中频分量再经过求导交叉相乘,求差,即为有用的语音信息。

图3.1 FPGA中频解调

3.2单片机控制

图3.2单片机发送流程图

4.系统测试

1.整体测试。

测试功能收到7个电台,基本实现所要求功能。

2.误差分析

有些电台接受不了,或者声音不清晰经分析原因有两个:

1)AD由于是欠采样对对信息完整度有影响。

2)天线接受信号携带的干扰信号并没有完全滤除造成干扰。

5.设计总结

本作品FPGA和430为核心部件,通过控制本振频率,从而选定不同的电台信号,经过混频产生10.7M频率信号,再经过FPGA解调,功放放大还原成声音。在设计中,我们尽量采用低功耗器件,力求硬件电路的经济性和精简性,充分发挥软件控制灵活方便的特点,来满足设计要求。

评论