时钟的抖动测量与分析

时钟是广泛用于计算机、通讯、消费电子产品的元器件,包括晶体振荡器和锁相环 ,主要用于系统收发数据的同步和锁存。如果时钟信号到达接收端时抖动较大,可能出现:并行总线中数据信号的建立和保持时间余量不够、串行信号接收端误码率高、系统不稳定等现象,因此时钟抖动的测量与分析非常重要。

,主要用于系统收发数据的同步和锁存。如果时钟信号到达接收端时抖动较大,可能出现:并行总线中数据信号的建立和保持时间余量不够、串行信号接收端误码率高、系统不稳定等现象,因此时钟抖动的测量与分析非常重要。

时钟抖动的分类与定义

时钟抖动通常分为时间间隔误差(Time Interval Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cycle to cycle jitter)三种抖动。

TIE又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量。理想时间位置可以从待测试时钟中恢复,或来自于其他参考时钟。Period Jitter是多个周期内对时钟周期的变化进行统计与测量的结果。Cycle to cycle jitter是时钟相邻周期的周期差值进行统计与测量的结果。

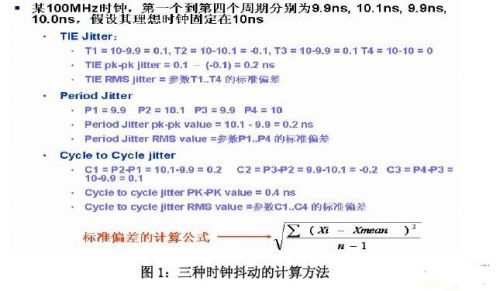

对于每一种时钟抖动进行统计和测量,可以得到其抖动的峰峰值和RMS值(有效值),峰峰值是所有样本中的抖动的最大值减去最小值,而RMS值是所有样本统计后的标准偏差。如下图1为某100M时钟的TIE、Period Jitter、Cycle to Cycle jitter的峰峰值和RMS值的计算方法。

时钟抖动的应用范围

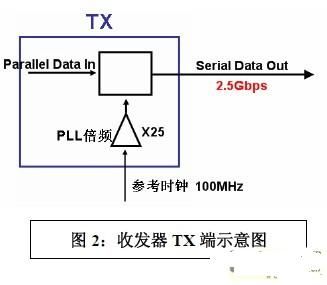

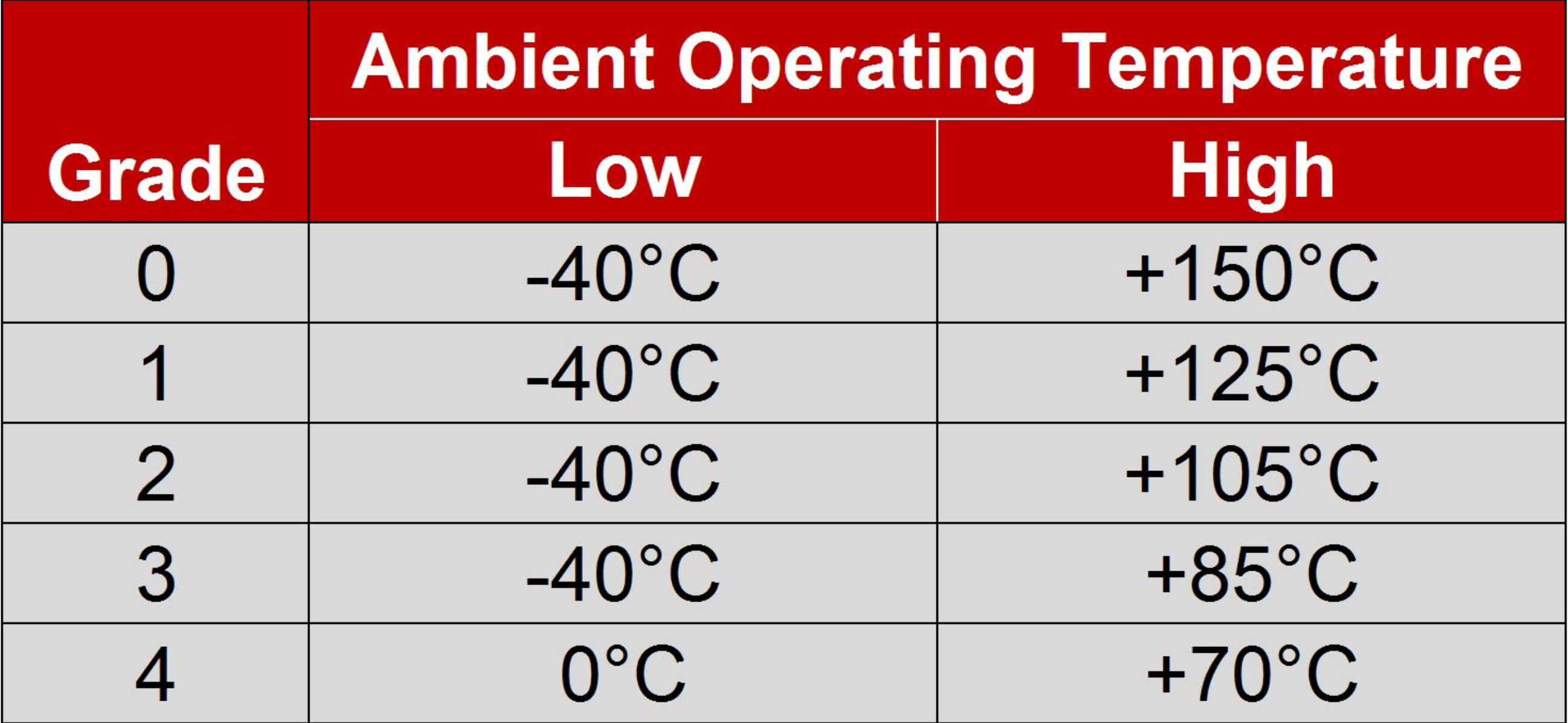

在三种时钟抖动中,在不同的应用范围需要重点测量与分析某类时钟抖动。TIE抖动是最常用的抖动指标,在很多芯片的数据手册上通常都规定了时钟TIE抖动的要求。对于串行收发器的参考时钟,通常测量其TIE抖动。如下图2所示,在2.5Gbps的串行收发器芯片的发送端,参考时钟为100MHz,锁相环 25倍频到2.5GHz后,为Serializer(并行转串行电路)提供时钟。当参考时钟抖动减小时,TX输出的串行数据的抖动随之减小,因此,需要测量该参考时钟的TIE抖动。另外,用于射频电路的时钟通常也需测量其TIE抖动(相位抖动)。

25倍频到2.5GHz后,为Serializer(并行转串行电路)提供时钟。当参考时钟抖动减小时,TX输出的串行数据的抖动随之减小,因此,需要测量该参考时钟的TIE抖动。另外,用于射频电路的时钟通常也需测量其TIE抖动(相位抖动)。

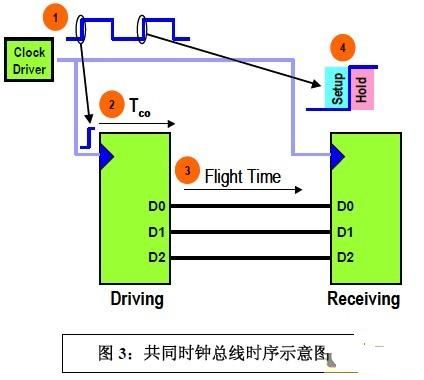

在并行总线系统中,通常重点如在共同时钟总线(common clock bus)中(如图3所示),完整的数据传输需要两个时钟脉冲,第一个脉冲用于把数据锁存到发送芯片的IO Buffer,第二个脉冲将数据锁存到接收芯片中,在一个时钟周期内让数据从发送端传送到接收端,当发送端到接收端传输延迟(flight time)过大时,数据的建立时间不够,传输延迟过小时,数据的保持时间不够;同理,当这一个时钟的周期值偏大时,保持时间不够;周期值偏小时,建立时间不够。可见,时钟周期的变化直接影响建立保持时间,需要测量period jitter和cycle to cycle jitter。关于共同时钟总线的时序分析的详细讲解,请参考Stephen H. Hall、Garrett W. Hall和James A. McCall写的信号完整性分析书籍:《High-Speed Digital System Design》。

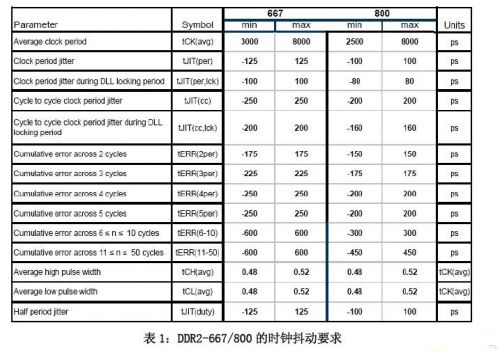

另外一种常见的并行电路-源同步总线(Source Synchronous bus),通常也重点测量period jitter和cycle to cycle jitter。比如DDR2就属于源同步总线,在Intel DDR2 667/800 JEDEC Specification Addendum规范中定义了时钟的抖动测试包括周期抖动和相邻周期抖动,分别如表格1中tJIT(per)和tJIT(cc),此外,还需要测量N-Cycle jitter,即N个周期的相邻周期抖动,比如表格1中tERR(2per)是连续2个周期的周期值与下2个周期的周期值的时间差,tERR(3per)是3个周期组合的相邻周期抖动,依此类推。

时钟抖动的来源和分解

时钟的抖动可以分为随机抖动(Random Jitter,简称Rj)和固有抖动(Deterministic jitter),随机抖动的来源为热噪声、Shot Noise和Flick Noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动;固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。

和串行数据的抖动分解很相似,时钟的抖动可以分为Dj和Rj。但不同的是,时钟的固有抖动中通常只有周期性抖动(Pj),不包括码间干扰(ISI)。当时钟的上下边沿都用来锁存数据时占空比时钟(DCD)计入固有抖动,否则不算固有抖动。

时钟抖动测量方法

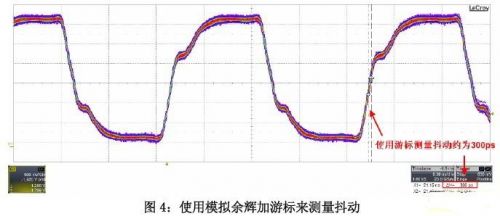

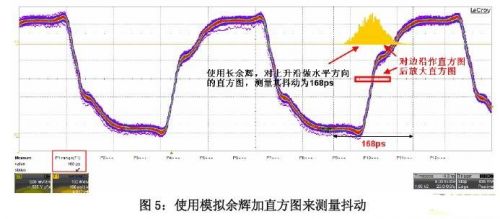

在上个世纪90年代,抖动的测量方法非常简单,示波器触发到时钟的一个上升沿,使用余辉模式,测量下一个上升沿余辉在判定电平上(通常为幅度的50%)的水平宽度。测量水平宽度有两种方法。

第一种使用游标测量波形边沿余辉的宽度,如下图4所示。由于像素偏差或屏幕分辨率(量化误差)会降低精度,而且引入了触发抖动,所以这种方法误差较大。

第二种使用直方图,对边沿余辉的水平方向进行直方图统计,如下图5所示。测量直方图的最左边到最右边的间距即为抖动的峰峰值(168皮秒)。这种方法的缺点是:引入了示波器的触发抖动;一次只测量一个周期,测试效率低,某些出现频率低的抖动在短时间内不能测量到。

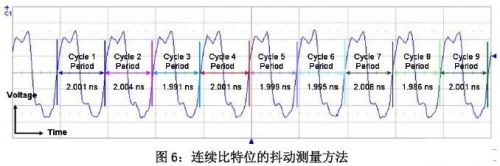

随着测试仪器技术的发展与进步,目前,示波器的抖动分析软件不再是测量一两个周期波形后分析抖动,而是一次测量多个连续比特位,计算与统计所有比特位的抖动,测量的数据量非常大、效率非常高。如下图6所示为某50MHz时钟的Period抖动测试,示波器的抖动测试软件可以一次测量所有周期的周期值,计算出抖动的峰峰值与有效值。

将已测量的每个周期的抖动值做直方图,可以统计大数据量的抖动的峰峰值和RMS值,如下图7所示为某时钟周期抖动的直方图分析,样本数量为103k个i,周期抖动的峰峰值为80.45皮秒,周期抖动的RMS值为9.25皮秒。

相位噪声与TIE抖动

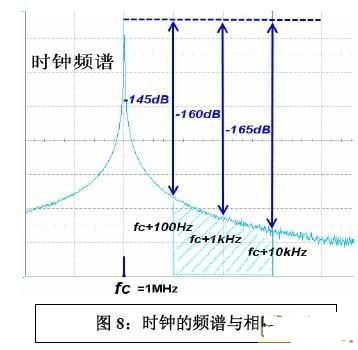

在一些时钟芯片的数据手册上规定了相位噪声(phase noise)的指标要求,相噪可以理解为TIE抖动在频域的表达方式,通常是使用某些频谱仪或相噪测试仪测量出来的,单位通常为dBc/Hz,比如某频率为1MHz的晶振的相噪为:

-145dBc/Hz @100Hz -160dBc/Hz @1kHz -165dBc/Hz @10kHz

如图8所示为该时钟的频谱,在频点fc+100Hz 的功率与fc频点(即时钟频率)的功率的比值取对数后为-145dB,在频点fc+1kHz的功率与时钟频率的功率之比为-160dB,在频点fc+10kHz的功率与时钟频率的功率之比为-165dB。在安装了相噪分析软件的频谱仪(或者相噪仪)上,通过对图8的阴影部分的求面积后进行简单运算,可以得到该时钟从100Hz到10kHz的TIE的RMS抖动值。对于某些精准的晶振,在某频段内的RMS抖动可以小于几百fs。由于实时示波器的抖动噪声基底大约在2ps左右,对于这类晶振的抖动测试,无法使用实时示波器的测量到,必须使用频谱仪或相噪仪测量。关于相位噪声与TIE抖动的换算,可以参考相噪测试仪厂商的技术图8:时钟的频谱与相噪文档。

时钟抖动的分析

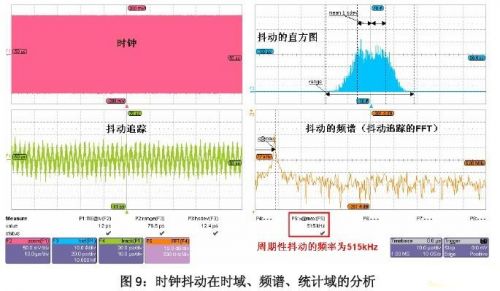

在时钟抖动测量时,可以在三个域分析抖动,即在时域分析抖动追踪(jitter track/trend)、在频域观察抖动的频谱、在统计域分析抖动的直方图。如下图9所示,左上角的F2为某100MHz时钟,P1是时钟的TIE参数测量;右上角的F3是TIE抖动的直方图,直方图不是高斯分布,可见时钟存在固有抖动。

左下角的F4为TIE track(即TIE抖动随时间变化的趋势),从TIE Track中可以看到周期性的变化趋势;右下角的F5是F4的FFT运算,即抖动的频谱,频谱的峰值频率为515kHz,说明该时钟的周期性抖动(Pj)的主要来源为515kHz,找到频点后,可以查找电路板上主频或谐波为该频率的芯片和PCB走线,进一步调试与分析。

评论