以高算力和超低功耗赋能MCU,瑞萨为AIoT应用增添新活力

——访瑞萨电子中国 产业解决方案中心

本文引用地址:http://www.amcfsurvey.com/article/201905/401006.htm高级总监徐征作者/王莹《电子产品世界》编辑

编者按:物联网潜力巨大,加上近年人工智能的兴起,AIoT(人工智能物联网)成为了新的热点。MCU作为传统的嵌入式处理器,似乎难以涉足高算力的AI应用。不过,瑞萨在嵌入式行业首开先河,提出了e-AI(嵌入式人工智能)解决方案,并带来了两大核心技术——DRP动态可配置处理器技术和SOTB超低功耗工艺,以期为AIoT的应用提供重要的附加价值。

1 e-AI解决方案出炉

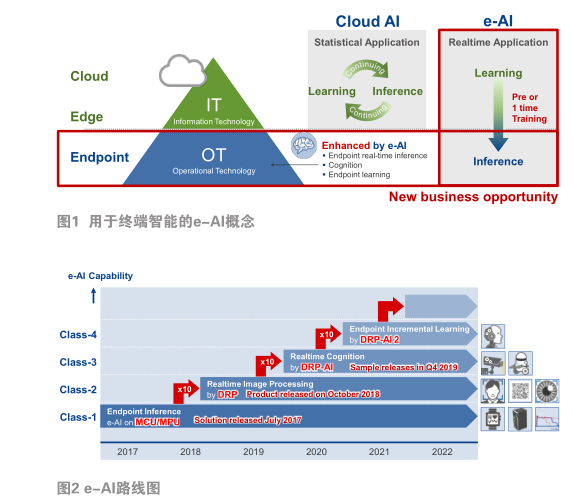

目前绝大部分产品的AI学习与推理是在云端进行的。在OT(操作技术)里面的终端产品或者设备,要到云端去做学习与分析,可能会造成网络延迟、带宽拥挤、网络安全性和功耗等问题。为此,瑞萨提出了e-AI解决方案(如图1),可以通过终端学习AI模型,实现实时、安全和低功耗的终端智能化。

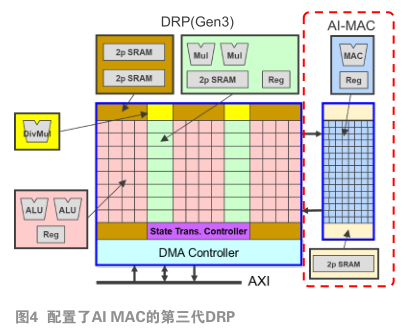

2017年7月,瑞萨首次公布e-AI方案,通过e-AI翻译器,把客户的AI模型翻译成C语言,然后在瑞萨RX系列MCU里实现AI终端的推理功能(如图2)。

2018年10月,第二代e-AI方案问世,通过把瑞萨独有的DRP技术做在芯片中,去实现DRP的e-AI解决方案。DRP即动态可配置处理器,顾名思义,客户可以按自己的需要,按不同的时间把DRP的硬件逻辑编程,实现并行的数据处理。DRP技术非常适合图像处理。

接下来,瑞萨在2019年第四季度将推出第三代e-AI解决方案,这是配置能力更强大的 DRP AI芯片,在器件中额外配置了AI MAC(乘加电路),特别适合卷积神经网络(CNN)。

第四代产品DRP AI 2也在规划当中,目的是实现在终端的增量学习功能。

2 DRP巧妙提升算力

DRP是瑞萨独有的技术。在同等功耗的前提下, 载有DRP技术的处理器比目前市场上常用的MCU、DSP或FPGA的处理能力高十倍或百倍,这意味着在相同的处理能力下,DRP的功耗比其他处理器低很多。

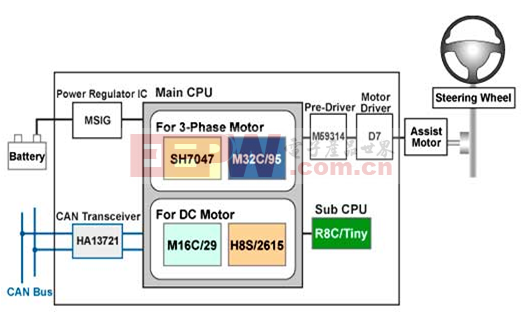

DRP的目标应用场景包括智能工厂、智能家居和智能基础设施。例如在工业控制的预维护中,e-AI应用方案可以通过一些学习完的数据,通过在电机上的加速度传感器去分析判断从传感器收集来的信息是否正常,然后再传送到控制中心或控制系统。这样可以大大改善生产效率,避免停机,同时也可以降低维护维修的成本。

另外一个应用场景是生物认证,例如机场或者口岸的出入境检查站,或者是办公楼的门禁系统。

DRP的结构主要包含多组并行阵列可编程的处理单元,加上存储器和DMA控制器(如图3)。DRP是动态可配置处理器,可以根据用户编程,能够做到从一个时钟周期到下一个时钟周期动态地改变其处理电路的配置,实现并行处理不同的算法。对于图像处理这种应用是非常适合的,可以做到每个时钟周期少于1 ns。

AI的深度神经网络(DNN)包含几个不同的处理层,诸如卷积层、池化层和全连接层等。因为DRP的独有特性能够满足卷积神经网络(CNN)所需要的多并行处理要求, 因此非常适合作为卷积神经网络的AI加速器。

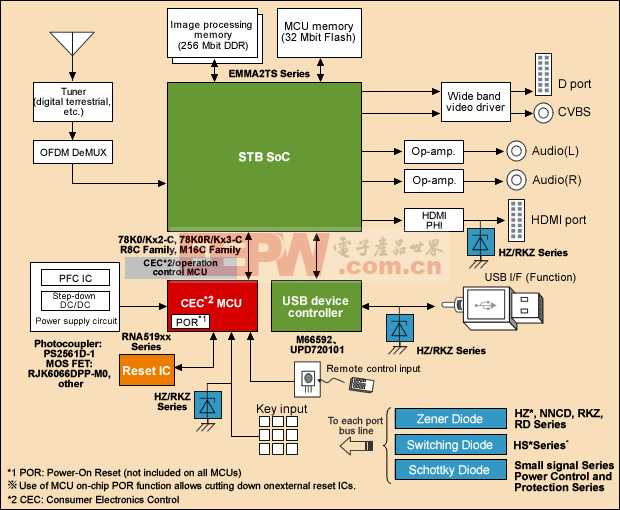

即将推出的第三代DRP配置了AI MAC(如图4),里面有多组快速处理单元,能实现有效的快速计算。卷积层里本身需要处理大量的数据,同时卷积层里的数据需要不断成立权重,然后再重复去计算,因而需要快速地去做乘法或加法。AI MAC结构可以满足卷积层里大量的复杂计算。

除了AI MAC硬件部分,第三代DRP也可以处理其他处理层的数据,例如也可以做动态可编程,可以把汇聚层里系统的计算合起来用。

通过对比一个500 MHz时钟频率的CPU,和第二代DRP,进行Canny边缘侦测算法的运算。500 MHzCPU需要140 ms;但DRP尽管只有40 MHz,却只用了10.4 ms,可见处理速度快十倍以上。

3 SOTB工艺实现了超低功耗

SOTB(Silicon On Thin Buriedoxide)是瑞萨研发的超低功耗的工艺技术,可以实现无掺杂的晶体管。无掺杂结构可以降低晶体管淤积特性变化。对比传统的平面式晶体管的淤积特性变化,这种无掺杂通道和结构可以将特性变化减低2/3。减小晶体管的淤积特性变化,就可以在超低电压下,例如0.5 V进行稳定的操作,同时也可以大大降低工作电流与待机电流。

SOTB在特定条件下,电流的消耗只是传统MCU的1/10。如果说传统方案是低功耗方案,SOTB就是超低功耗的方案,有望实现无电池系统。例如,传统MCU通过3 V的纽扣电池供电,间隔性侦测传感器的信号采集,再把信息上传到云端。如果这些任务占用1%的工作周期,一个月后系统就可能没电了。如果换到0.1%的工作周期,这个系统能工作一年左右。但是如果采用SOTB技术做成的MCU,在特定条件下可以连续工作十年。因为SOTB本身需要的电流非常低,3 µA就足够了。

SOTB的路线图有三个阶段。

第一阶段,在2019年下半年将会在中国市场正式发布,届时会做产品的介绍推广。目标应用场景是一些需要经常更换电池,或电气维护的应用。

第二阶段是2021年左右,计划会把无线技术,诸如蓝牙加进来,来扩展应用场景,包括智能家电或智能楼宇,以及个人健康产品。

长远目标主要是在第三阶段,不但把无线技术加进去,同时也会把e-AI/DRP解决方案带到器件里,做成一个完整的AIoT方案,届时应用场景会变得更加多样,包括智慧农业、智能交通等。

4 嵌入式AI的应用案例

瑞萨还展示了三个应用案例。

第一个是3D手势识别,通过RX231的e-AI解决方案,提供手势数据的学习工具、录制工具、AI的学习工具。客户只需做很小的代码改动,无需重新编写复杂的算法,就可以达到很高分辨率的3D手势识别和控制。

第二是马达异常侦测。采用32位MCU——RX66T来实现电机控制,以及e-AI推理功能。通过配置在电机上的加速度传感器收集信号,再通过学习的数据来判断收集回来的信息是否异常,同时把计算的故障率在电脑上显示出来。

第三是通过DRP实现实时图像处理器。主控制器是RZ/A2M,其中配置了DRP。图像处理可能会分成很多不同的算法,收集完影像后还需要去分析,还要做影像的解码,牵涉到很多不同的算法,DRP的主芯片可以满足图像处理的复杂计算要求。可以并行处理不同的算法。

瑞萨还提供了一组数字:相比Arm Cortex-A9528 MHz处理器,带有DRP处理能力的RZ/A2M快了13倍。DRP另外一个优势是低功耗,因为第二代DRP的主频只有66 MHz,第三代为250 MHz,但是主频低并不代表性能会相对降低,低主频可以达到低功耗的效果,因为DRP可以实现并行数据处理,所以它的处理能力比主频高很多的MCU或MPU处理能力更强大,比A9处理器的处理能力快13倍。

5 热点问答

问:DPR跟FPGA或其他技术有何明显的区别?

答:DRP可以理解成一个FPGA与GPU的混合体。

FPGA是一个可编程的硬件,要运算一个非常复杂的算法,里面需要很多逻辑电路,整个器件需要做得很大。瑞萨独有的DRP硬件技术,优点在于是动态可编程的,通过DRP编译器,可以把C语言编译成DRP的硬件逻辑去运行算法。下一秒钟,又可以马上再把同一个逻辑电路重新编排,去运算另一种算法。

与FPGA相比,运行同一个很大的算法,就可以把这个大算法切开为十个不同的小算法,去并行处理。这样整个逻辑电路不需要像FPGA做得那么大,只有FPGA的1/5或1/10即可(具体取决于用户怎么去编硬件逻辑)。

同时DRP又是FPGA和GPU的混合产品。因为DRP本身除了可以编程,也比较像GPU,可以做并行处理。但是GPU不能重新再编程。

有个生动的比喻,DRP就像动画片里的变形金刚,针对不同的场景,既可以是MCU,也可以是GPU。

问:e-AI解决方案与DRP、SOTB技术的关系如何?

e-AI是AI的一个概念。e-AI在器件层的落脚点,第一步是DRP,未来会有SOTB来支持e-AI在5G、IoT或者可穿戴领域的应用。

现在的DRP更多的还是在传统领域中应用,未来再加上SOTB的配合,会有更广阔的低功耗AIoT应用。

问:DRP是否会用于所有MCU?

答:DRP本身是一个硬件架构,但DRP也不可能单独去工作,需要把它放进MPU或者MCU里,中间有一个DMA控制器(注:作为MCU与DRP中间的交换沟通)。

瑞萨不会把DRP放进全系列的MCU或MPU中,是有选择性的,这是因为整个市场是多样性的。因此瑞萨传统的GPMCU(通用MCU)还会继续推广。

DRP的目的是促进AI学习或推理功能,是用于处理能力较高的处理器中,所以会选择放在瑞萨中高端的LC、AC系列MPU中。例如,DRP第二代可放入528MHz主频的MPU中。未来的第三代DRP性能更强大,MPU里会带有双核1 GHz处理器,以完成AI的学习与推理功能。

本文来源于科技期刊《电子产品世界》2019年第6期第1页,欢迎您写论文时引用,并注明出

评论