Cadence与联电合作开发28纳米HPC+工艺中模拟/混合信号流程的认证

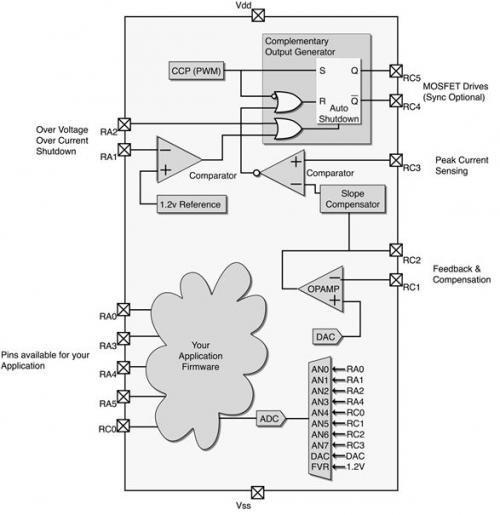

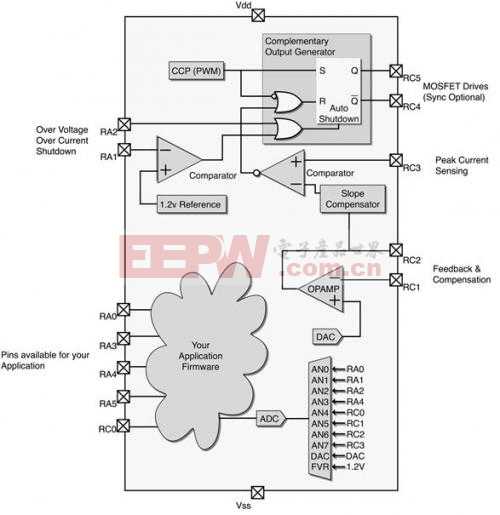

联华电子今(6日)宣布Cadence®模拟/混合信号(AMS)芯片设计流程已获得联华电子28纳米HPC+工艺的认证。 透过此认证,Cadence和联电的共同客户可以于28纳米HPC+工艺上利用全新的AMS解决方案,去设计汽车、工业物联网(IoT)和人工智能(AI)芯片。 此完整的AMS流程是基于联电晶圆设计套件(FDK)所设计的,其中包括具有高度自动化电路设计、布局、签核及验证流程的一个实际示范电路,让客户可在28纳米的HPC+工艺上实现更无缝的芯片设计。

本文引用地址:http://www.amcfsurvey.com/article/201908/403461.htmCadence AMS流程结合了经客制化确认的类比/数位验证平台,并支持更广泛的Cadence智能系统设计™策略,加速SoC设计的卓越性。 AMS流程具有整合标准组件数字化的功能,非常适合数位辅助类比的设计,是客户使用28纳米HPC+工艺,开发汽车、工业物联网和AI应用的理想解决方案。

经过认证的完整AMS流程包括Virtuoso®仿真设计环境(ADE),Virtuoso图形编辑器,Virtuoso布局套件,Virtuoso空间基础绕线器,Spectre®平行加速仿真器(APS),带有整合Xcelium®平行逻辑仿真引擎的Spectre AMS Designer,Voltus™-Fi客制化电源完整性解决方案,Innovus™实施系统,Quantus™寄生效应萃取解决方案和物理验证系统(PVS)。 该流程提供以下内容:

l前端设计:提供控角、统计和可靠性模拟; 电路和组件检查,以及类比和混合信号仿真和验证管理。

l客制布局设计:提供先进的电迁移和寄生感知环境,包括图形驱动布局和模块生成、线编辑器和引脚到主干的布线、符号置放、电子感知设计和压敏规则。

l后布局的寄生模拟和电迁移及电位降(EM-IR)分析与整合签核:包括寄生组件参数撷取,电路布局规则检查(DRC)和电路布局验证(LVS)检查。

l混合信号OpenAccess:在单个OpenAccess设计数据库上运行的Virtuoso和Innovus平台之间实现完全互动能力,使混合信号设计人员能够直接在Virtuoso环境内使用Innovus工具,且能无缝地执行数字区块的实作。

Cadence的客制化IC与PCB部门产品管理副总Wilbur Luo表示:「Cadence与联华电子合作,提供了经28HPC+技术认证的AMS整合设计流程,该技术基于Cadence业界领先的客制模拟/数字和签核以及验证平台。此认证推动了SoC设计的卓越性,使得联电的客户得以利用先进的功能工具组,进行电路设计、性能与可靠性验证、自动布局以及区块和芯片整合,使他们能够在汽车、工业物联网和AI应用芯片设计上更有十足的把握。」

联华电子量产就绪的28纳米HPC+工艺采用高介电系数/金属闸极堆栈技术,广泛支持各种组件选项,以提升弹性及符合效能需求,同时针对多样的产品系列,例如应用产品处理器、手机基频、Wi-Fi,数字电视 / 机顶盒,毫米波等具备高介电系数/金属闸极堆栈及丰富的组件电压选项、内存字节及降频/超频功能,有助于系统单芯片设计公司推出效能及电池寿命屡创新高的产品。

联华电子硅智财研发暨设计支持处林子惠处长同时表示:「透过与Cadence的合作,结合Cadence AMS流程和联电设计套件,开发了一个全面而独特的设计流程,为我们在28纳米HPC+工艺技术的芯片设计客户提供可靠与高效的流程。凭借此流程的功能优势,提供用户详细说明,以利客户透过联华电子的流程提升生产力,可更快地将下一代的创新产品推向市场。」

评论