FPGA到高速DRAM的接口设计(04-100)

—— FPGA到高速DRAM的接口设计

FPGA做为系统的核心元件正在更多的用于网络、通信、存储和高性能计算应用中,在这些应用中都需要复杂的数据处理。

本文引用地址:http://www.amcfsurvey.com/article/80852.htm所以,现在FPGA支持高速、外部存储器接口是必须遵循的。现在的FPGA具有直接接口各种高速存储器件的专门特性。本文集中描述高速DRAM到FPGA的接口设计。

设计高速外部存储器接口不是一件简单的任务。例如,同步DRAM已发展成高性能、高密度存储器并正在用于主机中。最新的DRAM存储器—DDR SDRAM,DDR2和RLDRAM II支持频率范围达到133MHz(260Mbits/s)~400MHz(800Mbits/s)。

因此,设计人员往往会遇到下列问题:DQ—DQS相位管理、严格的定时限制、信号完整性问题和同步开关转换输出(SSO)噪声。另外一些板设计问题会延长设计周期或强迫接受降低性能。

DQ-DQS相位关系管理

DDR SDRAM靠数据选通信号(DQS)达到高速工作。DQS是用于DQ线上选通数据的非连续运行来保证它们彼此跟踪温度和电压变化。DDR SDRAM 用片上锁延迟环(DLL)输出相对于相应DQ的DQS。

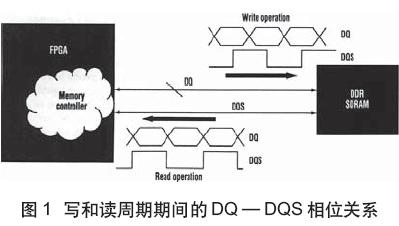

DQ和DQS信号间的相位关系对于DDR SDRAM和DDR2接口是重要的。当写DRAM时,FPGA中的存储器控制器必须产生一个DQS信号,此信号是中心对准在DQ数据信号中。在读存储器时,进入FPGA的DQS是相对于DQ信号的沿对准(图1)。

评论