一款效率高达80%且功率损耗不足1W的3A、1.2VOUT 线性稳压器(07-100)

引言

本文引用地址:http://www.amcfsurvey.com/article/81737.htm由于稳压器对压降的要求、效率的低下、因稳定性需要而对输出电容器过于严格的要求以及启动时太大的浪涌电流等原因,在大电流 (>1A) 低压降电压应用中采用线性稳压器一直都是个难题。TI 推出的具有双输入轨的 TPS74x01解决了上述问题。

线性稳压器拓扑概述

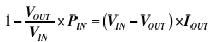

大电流应用中线性稳压器的主要缺点是效率较低,其效率可以通过 VOUT/VIN 计算得出。线性稳压器的功率损耗 (PLOST) 主要来自其封装,该功率损耗可以通过如下公式计算得出:

TO-263 或 D2PAK 封装是可用于线性稳压器的最大表面贴装封装。不计气流的话,该封装的最大功耗大约为 2.75W(假设该封装与一块较大的铜板焊接在一起用于散热)。带有 PMOS 旁路元件的大多数大电流低压降线性稳压器的最小输入电压范围为 2.5V~2.7V,其不但可以为内部 LDO 驱动电路供电,而且还足以驱动 PMOS FET 来提供较高的输出电流。

由于额外气流和/或需要对稳压器所产生的热量进行外部散热,因此,在输出电压低于 1.8V 和输出电流大于 2.5A 时使用带有 PMOS 旁路元件的线性稳压器就会显得不便,并且成本也会增加。

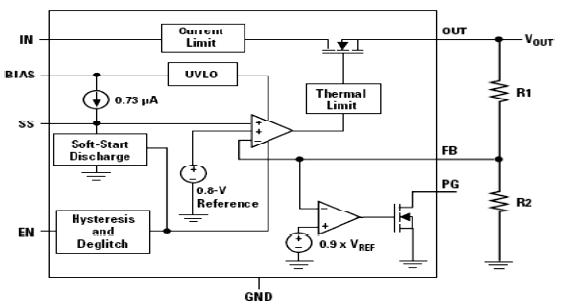

因为 NMOS FET 与具有相同电流速率的 PMOS FET 相比,一个较低的 rDS(on) 是其固有的特性,所以 NMOS FET 旁路元件只需要更低的 VIN-VOUT 压降即可提供相同强度的电流。但是,基于 NMOS 的稳压器的源极跟随电路结构要求 FET 门极至少为一个高于输出电压的阈值压降(一般为 1V)。稳压器需要一个内部充电泵来提供一个更高的栅极驱动电压,或是一个由电路中现有的 5V 或 3.3V 偏置电源产生的二次低功耗输入轨。这也就是设计基于 NMOS 旁路元件的双输入轨 TPS74x01 系列线性稳压器的原因。

压降

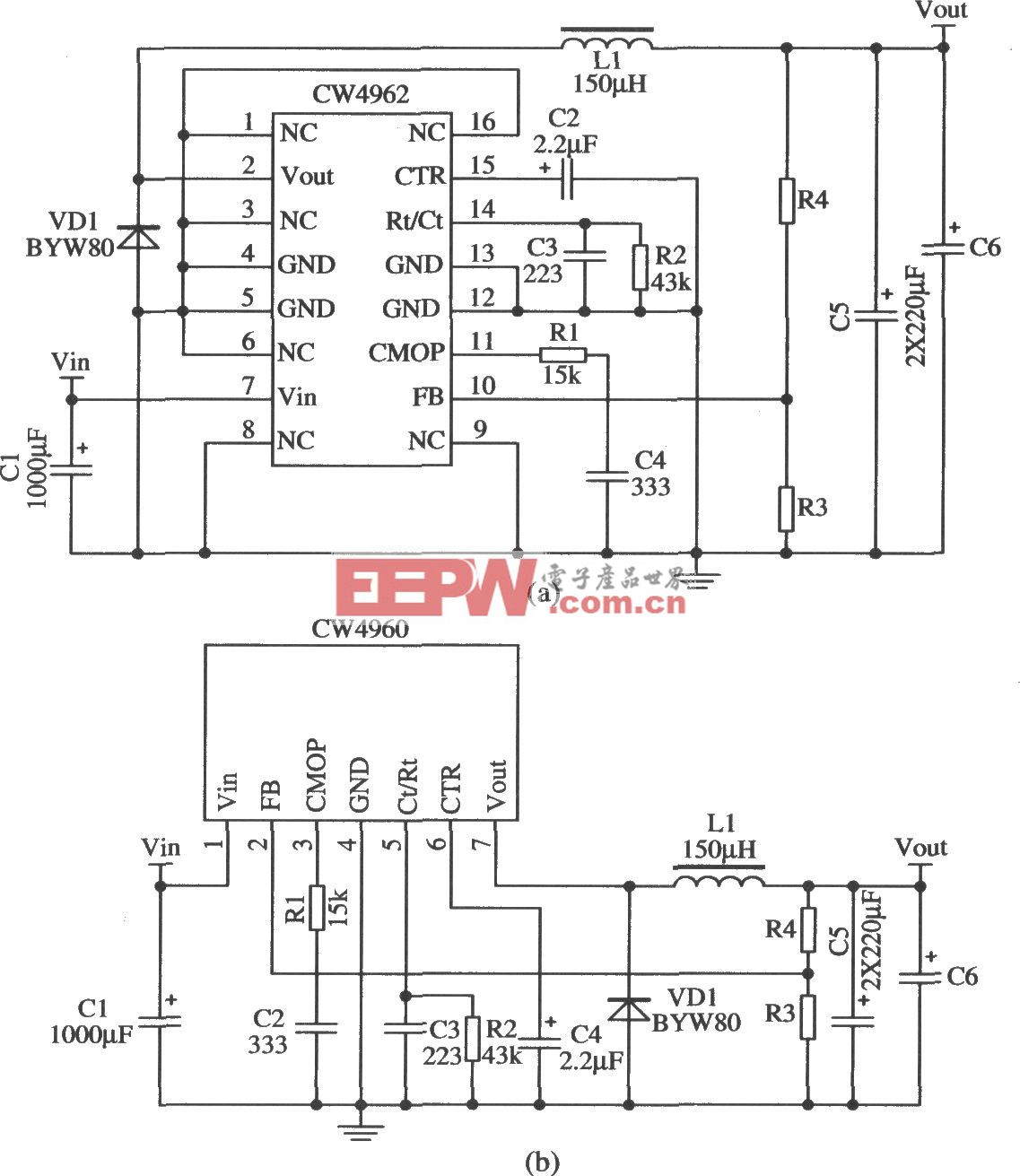

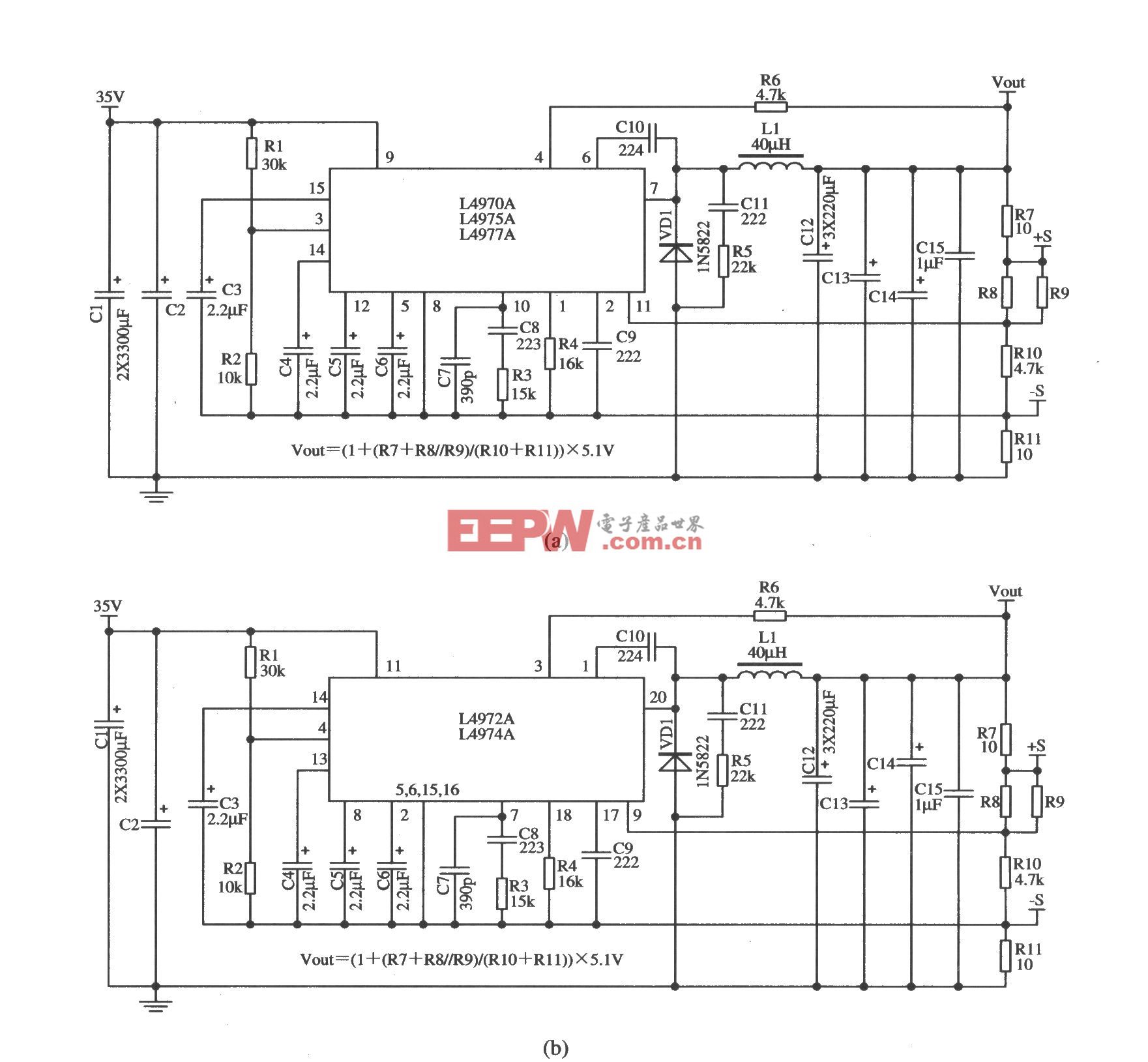

如图 1 所示,TPS74x01线性稳压器有两个输入电压,其中一个用来提供弱电流偏置电压以驱动控制 NMOS 旁路元件的内部电路,另一个用来进行二次功率输入。所有的内部电路均使用较高的偏置电压运行,旁路元件可以通过一个低压输入源实现稳压。实际上,输入功率 IN 只受制于输出电压和器件压降。

TPS74x01 有两种不同规格的压降。第一种规格为 VIN 压降,其专门针对那些希望通过采用一个外部偏置电压来实现较低压降的用户。该规格的稳压器偏置电压大于输出电压,至少为 1.62V。此类应用中,FPGA 收发器一般使用低纹波、1.2V 和 3A 的电源轨,该收发器内部 1.5V 和3.3V的开关电源分别提供输入电压和偏置电压。在该结构中,55℃时功耗为1.9W的 3×3mm QFN 封装功耗仅为 (1.5V-1.2V)×3A=0.9W,从而达到 1.2V/1.5V=80% 的效率。

评论