降低告诉DSP系统设计中的电源噪声(05-100)

具有较高时钟率和速度的高速DSP系统设计正在变得日益复杂。结果,增加了噪声源数。现在,高端DSP的时钟率(1GHz)和速度(500MHZ)产生可观的谐波,这些是由于PCB线迹的作用如同天线所致。由此引起的噪声使音频、视频、图像和通信功能降低并对达到FCC/CE商标认证造成问题。为了降低电源噪声,对于高速DSP系统设计人员来讲,识别和找出可能的噪声原因以及采用良好的高速设计实践是关键。本文说明交扰、锁相环(PLL)、去耦/体电容器在降低噪声中的重要性。

本文引用地址:http://www.amcfsurvey.com/article/91454.htm降低交扰

交扰是一个重要的噪声源。在高速系统中,信号地通路依赖于工作频率。对于低速信号(<10MHZ),电流经过最小电阻地通路(最短通路)返回到源。

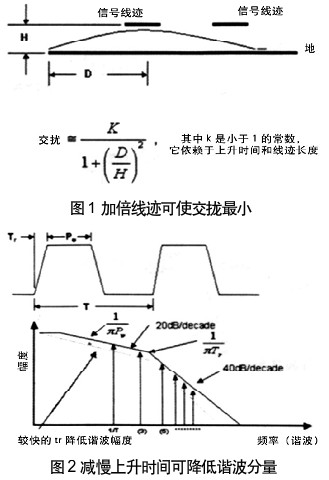

在10MHZ以上,情况就不同。经电流最小电感地通路返回。重要的是返回信号以电流分布传播(图1),这意味着相邻信号的返回通路可能容易重叠,导致交扰。

降低交扰的技术有:线迹间距加大,增加地线,降低谐波分量和线迹端接技术。

在高速DSP系统中,加倍信号间的线迹间距,可降低环路重叠,使交扰降低4倍。对于差分信号(Ethernet或USB),建议间距所产生的信号对应具有所需的匹配阻抗。另外,关键信号(即时钟)应屏蔽,路由信号在电源和地平板之间的内层,或把一个地平板放置在关键信号下面层上。

在再制板上加信号线时,应包括一个并联地线。这可能提供高速电流返回通路并在电流环路中产生最小面积。这个附加的通路,确保返回电流不产生大的环路和拾取噪声。

在降低交扰时,评价快速沿所引起的谐波和干扰是重要的。例如,在线迹上增加串联终端电阻器,会使上升时间(Tr)减慢,这是有效地降低谐波分量的方法。噪声幅度曲线在低频能较好地衰减谐波分量(图2)

线迹可做为传输线(在上升时间Tr小于2倍传播延迟时)。因此,应保持线迹尽可能的短。若线迹的长度足以做为传输线,则用串联终端(电阻器与输出驱动器串联)或并联终端(在负载处电阻器到地)接线。若电阻器与所用线迹PCB阻抗匹配,则可以降低传输线反射和瞬变。

锁相环

锁相环(PLL)是另一个重要的噪声源。在某些DSP中正日益采用模拟和数字版本PLL(图3)。隔离到PLL电源时,用π形滤波器去除高频噪声是有效的。但它对去除低噪声作用不大,需要用多级滤波器网络。然而,在快速开关电路中,一个低压降(LDO)稳压器是更适合的,因为这种器件在低频具有高电源抑制比(PSRR)。若设计的系统运行在噪声环境(如汽车、电/机装置),具有较大的低频瞬变,则应选择高PSRR稳压器。

锁相环相关文章:锁相环原理

评论