边界扫描与处理器仿真测试(05-100)

—— 边界扫描与处理器仿真测试

当前,PCB是越来越复杂,不言而喻,想要获得满意的测试覆盖范围也更困难了。而且每种测试方法都有其固有的局限性。于是,测试工程师们不得不另辟蹊径,将几种技术组合起来以达到他们所要求的测试覆盖范围。这正是IEEE 1149.1边界扫描(俗称JTAG)和微处理器仿真测试所追求的。边界扫描和处理器基仿真测试有各自的应用领域,每种技术都能达到某种程度的测试覆盖范围。然而将两种技术无缝地组合在一起,就有可能达到更高的总测试覆盖范围,是任何一种单独技术无法比拟的。

本文引用地址:http://www.amcfsurvey.com/article/91570.htm若将传统的JTAG结构性测试和处理器基功能仿真测试组合起来,提高了测试覆盖范围,从而可以简化测试,简化程度取决于所采用的其它测试方法,如电路内测试(ICT)、自动光学检查(AOT)、或飞行探针法。确实,即便工程上存在缺陷,如电路板上不合适的可测试性设计(DFT)性能等,也可以得到一定程度的弥补。

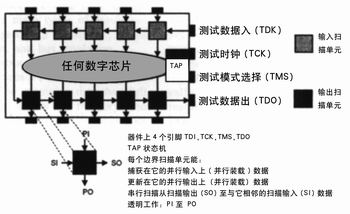

符合IEEE1149.1边界扫描标准的半导体器件,在器件四周有一组串行移位寄存器,边界扫描这个术语因此得名。在边界扫描芯片上,每个主输入信号和主输出信号都设置有一个称为边界扫描单元的多用途存储单元(图1).

图1 带边界扫描单元半导体器件的方框图

在PCB设计上,将各个芯片的边界扫描单元串接成并行输入,并行输出的移位寄存器。数据可在每个边界扫描单元的输入、输出上捕获,或串行地扫描通过整个单元链。这个链路称为边界扫描路径,或简称为扫描路径。

评论