利用频域时钟抖动分析加快设计验证过程(07-100)

—— Using frequency domain clock jitter analysis to speed up design certification process

引言

本文引用地址:http://www.amcfsurvey.com/article/92051.htm随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展。目前的重点是针对比特误码率,在时钟性能和系统性能之间建立直接联系。我们将探讨参考时钟的作用和时钟抖动对数据抖动的影响,并讨论在E5052B信号源分析仪(SSA)上运行的Agilent E5001A精确时钟抖动分析应用软件所配备的全新测量技术。该应用软件提供了前所未有的强大能力,可以对随机抖动(RJ)和周期抖动(PJ)分量超低RJ测量和实时抖动频谱分析,使您能够提高设计质量。我们还将对新解决方案的实时测量功能进行讨论,这一功能能够加快设计验证过程。

参考时钟在高速串行应用中的作用

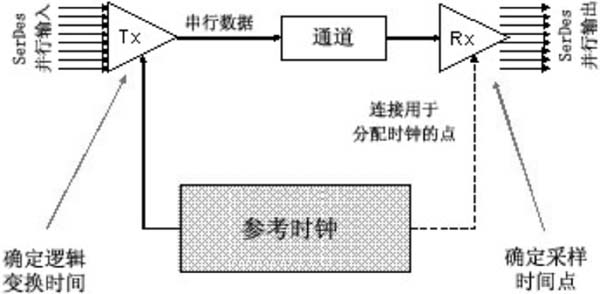

图1是参考时钟的主要分量。发射机通常将一组速率较低的并行信号转换成串行数据流。信号经过一条包括多个背板和电缆的传输通道进行传送。接收机通常会解释输入的串行数据,从中分离出时钟,再把串行数据重新转换成并行数据流。在许多诸如此类的说明中,参考时钟更多地被视为一种分量但不是主要分量,而在高速串行数据系统中,我们必须承认参考时钟是一种主要分量。通常,参考时钟的振荡速率远远低于数据速率,但它会在发射机中成倍增长。发射机使用参考时钟来确定串行数据流中的逻辑变换定时。发射的数据中包括参考时钟的特征。在接收机中可能会出现两种不同的情况。如果未分配参考时钟,则接收机会利用锁相环(PLL)从数据流中还原时钟――并利用该时钟定位采样时间点。如果已分配参考时钟,则接收机会同时使用数据信号和参考时钟来定位采样点。

图1 参考时钟的作用

评论