为您的转换器选择正确的时钟

时钟上的抖动和宽带噪声

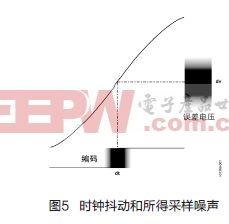

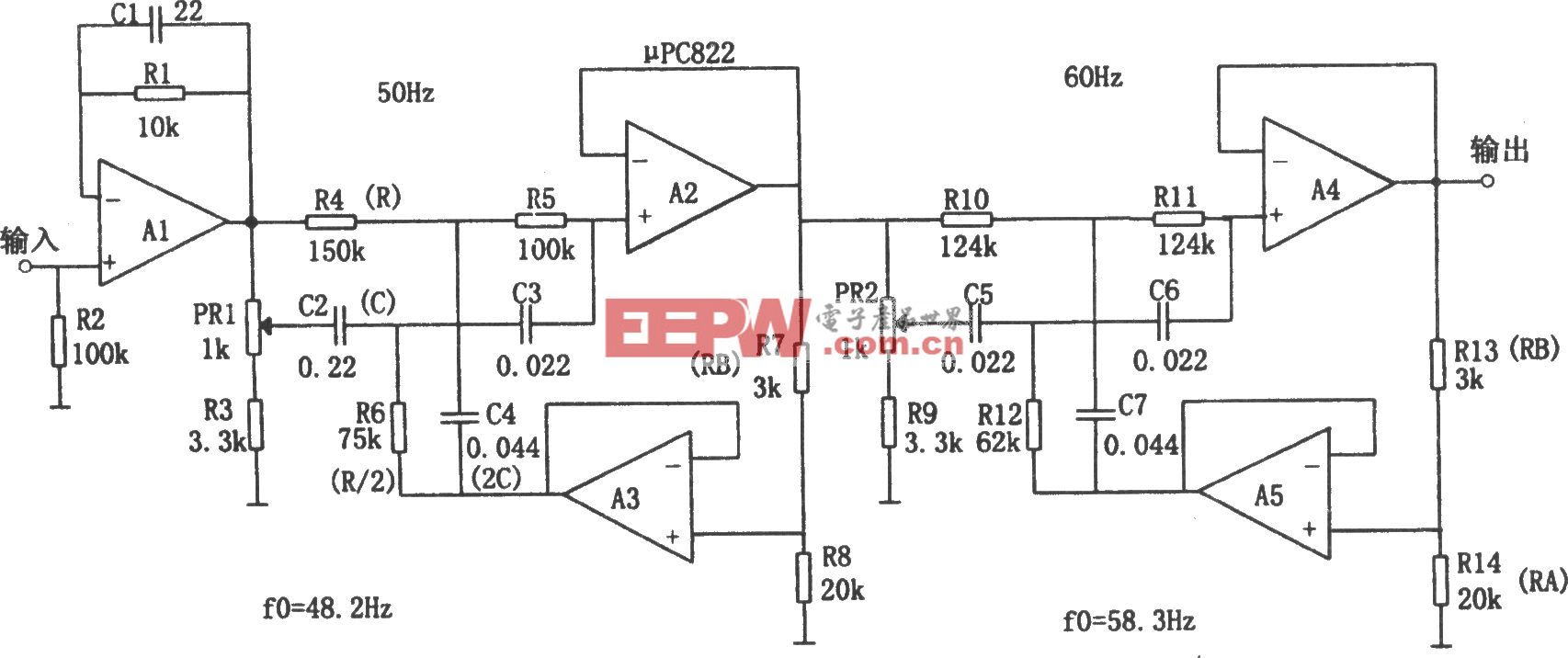

孔径抖动指孔径延迟中的样本间变化,在ADC输入中表现为频率相关噪声。对于高频模拟输入信号,抖动是采样过程中宽带噪声的主要来源。如图5所示,采样时钟上的噪声在所得采样信号上造成更多采样噪声。

图5显示了采样时刻中的误差是如何导致采样后电压值误差的。在数学上,采样后电压值误差幅度是由信号函数对时间的导数定义的。考虑一个正弦波输入信号,其中A是峰值幅度(通常假定为1),f是模拟频率,t是时钟抖动。

导数是

当余弦函数等于1时会产生最大误差,也就是在t = 0的时候。

从该图中我们可以看到dv是与抖动dt相关联的采样后电压值误差。为了让概念更清晰,如果我们将dv替换为Verr,将dt替换为ta(孔径误差),重新整理系数,则得到:

如果给定ta是均方根值,求导出的Verr也是均方根值。尽管这是在最大输入量时的误差,并且只代表上限而不是一个标称值,但这个简单的模型证明了惊人的准确性,而且对根据采样时钟抖动估算信噪比的降低很有用。

如公式所示,采样后电压值误差随输入频率和孔径抖动呈线性增加,所以在高频率时,时钟纯度变得极为重要。如上所述,采样是一个混频操作:输入信号乘以一个本振,或者一个采样时钟(在本例中)。因为在时间上的乘法是在频域的卷积,所以采样时钟的频谱与输入信号的频谱卷积。考虑到孔径抖动是时钟上的宽带噪声,它在采样后的频谱上显示为宽带噪声,在采样频率周围周期性地重复。值得注意的是,如果时钟上的噪声有色(非白色),则所得采样后频谱将具有由时钟频谱和模拟频谱卷积所定义的相似特性。

由于ADC编码输入有很高的带宽,时钟输入噪声的影响可以扩展至采样速率的很多倍并混叠到转换器的基带上。因此,这个宽带噪声会降低ADC的本底噪声性能。

其中:

A=均方根模拟输入

Verr=均方根电压误差

f =模拟输入频率

ta =孔径不确定度(抖动)

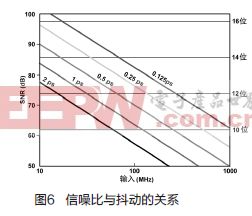

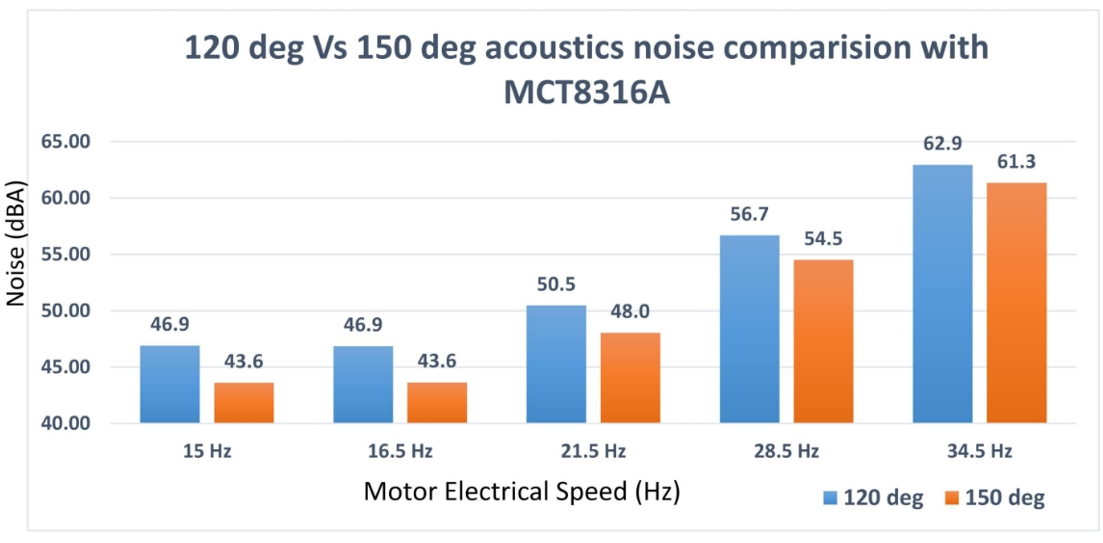

这个简单的公式为数据转换器在时钟方面的噪声性能提供了相当深刻的见解。图6涵盖了在不同分辨率(水平线)下,用该公式表示的具有理想、量化噪声限制性能的不同抖动值(斜线)的曲线图,它是基于模拟输入频率和信噪比要求来快速确定总系统抖动限制的一个有用的指导。应注意,该抖动表示时钟链内的总抖动,下文将显示其示例。

许多设计人员可能无法获得时钟抖动值,只能获得时钟相位噪声特性。这种情况下,假定噪声仅由高斯噪声组成,不包括杂散成分,如PFD(鉴频鉴相器)杂散。下一段落将讨论时钟杂散成分。由于相位噪声与时钟抖动之间存在直接关系,因此可将其相互关联起来。

本文引用地址:http://www.amcfsurvey.com/article/121371.htm

评论