数字控制可变增益放大器的优势

移动电话基站的性能和其它无线基础设施系统的性能取决于系统从与每个信号塔站连接的大量智能手机以及其它设备接收无线信号的好坏。提高接收器的信号与噪音比(SNR),加之提供一个宽泛的信号增益控制范围将保证各个基站可以提供一致性的性能,同时可最大限度地减少由于信号损失或噪音产生的影响。

本文引用地址:http://www.amcfsurvey.com/article/121381.htm在移动电话基站中,采用模拟信号或数字域的方式,可以解调和解码中频(IF)信号。目前,数字技术和高速模拟---数字信号转换器(ADC)方面取得的进展可以使得信号的接收通道直接采用数字信号的方法进行IF信号的转换。这种信号的转换方法通常称为IF的二次采样法,它相对于采用模拟信号解调方法的接收器系统,可极大地减少接收器使用部件的数量,同时降低了接收器系统的功耗和成本。

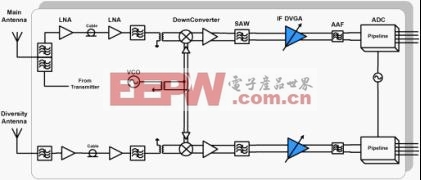

IF二次采样系统一般包括一个驱动AAF滤波器的数字控制可变增益放大器(VGA),该AFF滤波器依次将信号馈入高速模拟---数字信号转换器(ADC)中。数字处理ADC的输出信号,对VGA形成一个混合信号反馈回路,根据信号的强度进行增益调整(图1)。来自DSP的反馈信号调整增益量,将信号保持在最佳信号---噪音比和最小失真的“最清晰点。”

图1:接收器系统的一般性框图

Main antenna :主天线 Diversity antenna:分集式天线 LNA:低噪音放大器Cable:电缆

From transmitter:从发射机VCO:低压控制振荡器 Down Convert: 降频转换

SAW:表面声波 if DVGA:高线性度数字可变增益放大器

AAF :模拟抗混淆滤波器 ADC:模拟数字转换器 Pipeline:流水线

IF二次采样方法的核心是数字控制VGA。数字控制VGAs的多家供应商可供货各种型号、不同IF范围优化的数字控制VGAs。本文中,我们将使用最近发布的F1200型数字控制VGA,作为今天可以提供技术的一个实例。F1200型数字控制VGA是IDT公司提供的数字控制VGA系列产品中的第一个产品,它具有40至160兆赫的IF频率范围。未来的系列产品---F1206和F1207将分别提供150至260兆赫和230至300兆赫的频率范围。

F1200型数字控制VGA具有7位数控制接口(相对于其它供应商供货的5位或6位数字VGAs),使得增益的增量在-1至+22 dBm的范围内可设定为0.25dB。这种较细的粒状分级使得设计人员可以更好地优化系统的性能。同时,增益步进的精确度也非常紧密---小于0.1 dB的变化。

此外,F1200型数字控制VGA的芯片具有的噪音指数(NF)仅为2.6dB,大大低于其它具有竞争性解决方案芯片的噪音指数(NF)。芯片较低的噪音指数(NF)也会有助于简化系统的设计,因为可将增益的设定值保持在略低的数值,并由此表现为较低的信号失真。F1200型数字控制VGA芯片本身也提供了非常低的信号失真效果---IP3o达到+48dBm。芯片较低的噪音指数(NF)和低信号失真性同样可以简化后置VGA的滤波电路,由此减少了所使用元件的数量并降低了成本。此外,低信号失真性提供了增加的无寄生信号动态范围(SFDR),由此使得电路适用于广泛的应用范围。

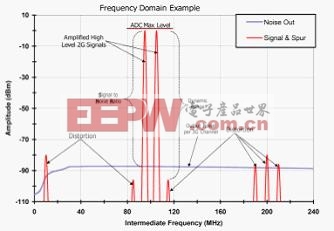

图2中的曲线图给出了2G和3G移动通信系统信号通道的典型性能特征。在图2的曲线图中,以特定的2G(GSM)的输入信号给出了输出信号。增益值会被调整致使2G信号放大到仅仅低于ADC最高水平。这些信号之间的互调导致三阶互调结果接近理想状态和输出信号。图中所示在频率的更远端二阶互调。此外,输出噪音以蓝色曲线表示。在ADC之前需要滤掉二阶互调和噪音,以避免混入到有用的波段信号中。F1200型数字控制VGA的IM2失真和增加的噪音都非常低,所以仅需要进行最低限度的滤波。三阶结果和波段内的噪音无法过滤掉,所以关键的是选择类似于F1200型数字控制VGA---具有非常低三阶失真的中频VGA。

图2:VGA输出端的信号、噪音和信号失真

Amplitude:(dBm) 幅度( 毫瓦分贝) Frequency Domain Example: 频域实例

Amplitude High Level 2G signals:2G信号高振幅signal to noise Ratio:信噪比

Distortion:失真 ADC Max level :模拟数字转换器最大值

Dynamic Range:动态范围 Output Noise Per 3G Channel:3G通道噪音输出 Noises out:噪音输出 signal &spur:信号和杂散

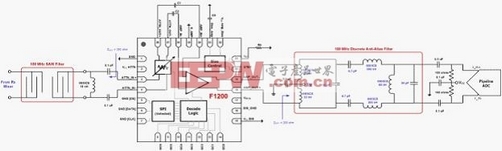

在实际接收信号通路中,接收到的信号通常通过混频器,降频转换频率,然后通过SAW(表面声波)滤波器,消除没有用的信号波齿(图3)。由此产生的信号将通过数字控制VGA。F1200型数字控制VGA的输入端提供有一个200欧姆的平衡输入阻抗,该阻抗也非常适合用于其它系统,该阻抗的使用代替了需要与元件进行匹配的外部阻抗。

200欧姆的输出端差分阻抗对ADC的接口也可进行很好的匹配,且设备的差分特性抵挡偶次乱真信号响应。较高阶的谐波在馈入ADC之前很容易被AAF滤波器过滤掉。

图3:从混频器输出端至ADC,BTS接收器的后端排列

100 MHz SAW Filter :100 MHz表面声波滤波器

From Rx mixer:从接受器混频器 GND:接地 ATTN IN:衰减输入 CS:片选 DATE:数据 CLK:时钟信号AMP in:放大器信号Bias AMP:偏置放大器 Bias control :偏置控制 SPI(untested):串行外设接口(未检测)Decode logic:逻辑解码

AMP out :放大器出 STGY:电子器件型号 DIG –GND:数据处理器接地 100 MHz Discrete Anti-Alias Filter:100 MHz消除锯齿波的AAF滤波器

Pipeline ADC:流水线类型的数模转换器

当ADC转换经过调整后的信号时,通常将经过转换的信号输入到主处理器或数字信号处理器,主处理器或数字信号处理器执行不同的算法,以进一步优化反馈的信号,从而在VGA中设定最佳增益值。

设计VGA电路板时,电路板的特征是要具有100欧姆的特性阻抗,电路板的布线尽可能短,与此同时长度,噪音、频宽和信号的损失得到优化。

F1200型数字控制VGA的500毫瓦较低的功率消耗也使得电路板的设计和耐热通道布局变得非常简单。无铅封装包括一个耐热垫,它通过印刷电路板的铜散热,因此无需添加散热片。

插图说明:

图1:在一个典型的基站接收器系统中,数字控制VGA放置在混频器之后。混频器由SAW滤波器驱动,并依次将信号馈入AAF滤波器,然后将信号输入到ADC。

图2:一个典型的直接变频信号路径波形给出了F1200型VGA的低本底噪音以及系统综合性的动态范围。

图3:在本接收信号的路径中,SAW滤波器整形输入信号,并将输入到数字控制VGA。调整增益后,VGA将信号输入到AAF滤波器,然后输入到ADC。信号转换后,ADC通常将数据传送主处理器或DSP模块,在将控制位数反馈至VGA前,进行进一步的处理。

模拟信号相关文章:什么是模拟信号

adc相关文章:adc是什么

混频器相关文章:混频器原理 数字滤波器相关文章:数字滤波器原理

评论