Synopsys音频子系统:打造完美声音

视频显示已经发展到高清、3D,怎样能够营造出“未被其人吸引,先被其声打动”的效果是很多做音频产品厂商苦思冥想的事情。现在各个厂商对于产品的上市时间要求都很严格,如何能够在短时间内开发出独具特色的产品成为制胜的关键。Synopsys推出的音频子系统DesignWare SoundWave Audio Subsystem抓住这一市场需求,应运而生。

本文引用地址:http://www.amcfsurvey.com/article/131375.htm何谓完整的音频IP子系统?

新思科技高级产品推广经理Henk Hamoen介绍说,Synopsys此次推出的音频IP子系统包括了预先验证过的内置硬件、集成化软件、虚拟和FPGA原型以及一个配置工具。

新思科技高级产品推广经理Henk Hamoen

图一 完整的音频IP子系统

具体包括以下组件:32位Design Ware ARC音频处理器,标准数字接口,模拟编解码器,一个可支持来自Dolby、DTS和SRS的最新格式的软件音频编解码器综合库;包含一个集成媒体流框架的完整的软件环境。

比起市场上其他的解决方案,有的还需要用户去探明缺失的组件,有的需要更多的时间去进行系统调试和验证,这样就增加了客户的时间成本和风险,如果采用此款完整的音频IP子系统,能够在设计集成和验证工作量方面节省两人年的时间,以下工作无需再做,比如:探明应用需求,执行硬件/软件功能划分,对来自不同供应商的IP进行选择和配置,硬件/软件架构的IP集成与开发,主机接口软件开发,功能、集成与性能测试以及SoC设计流程。原来需要几周时间来配置音频子系统现在可以缩短到几个小时,如此“速食”,号称“plug in”(放入即用),

完全可配置助力产品实现差异化

在这个什么产品都讲究用户体验的时代,如何快速打造出与众不同的产品成为制胜关键,Synopsys的这款音频IP子系统通过将多个IP模块与软件集成到一个预先验证的子系统,给设计师带来了一套可配置的、在SoC中现成可用的音频解决方案,在满足SoC所要求的音频功能的同时工程师可以使用CoreAssemble工具配置以下内容:数字接口(I2S和S/PDIF)的数量及其参数;连接到模拟IP的接口数量及参数;ARC音频处理器配置选项;所需的软件组件(解码器、编码器和后处理功能);时钟管理选项和复位管理选项等,帮助客户实现其产品在市场上的独一无二。

Henk介绍,此系统中ARC处理器有单核和双核两种选择,如果用在比较简单的产品中,可以选择单核,如果需要更复杂的音频处理能力,可以选择双核。如果选择双核,客户可以根据需要来配置这两个内核的使用,可以将其中一个内核做配置,另一个内核交给自己客户再继续做配置以更好的实现差异化;或者可以所有的任务分配到两个内核上,这样可以减轻处理器的负担。

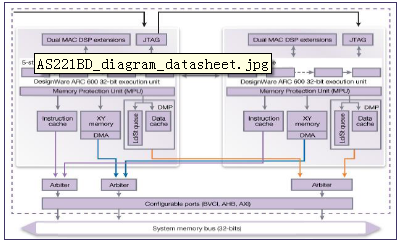

图二 ARC处理器的双核架构

在提到此解决方案与其他竞争产品的比较的时候,Henk列举了3个优势:

1、 此方案能实现低功耗,用在MP3解码时仅需0.30mW,而且体积很小,只有0.21mm2

2、 专门的软件环境和EDA设计工具,让客户使用起来得心应手,减少了在软件开发方面的时间和人工成本。

3、 访问内存,延迟容忍度大。虽然很多解决方案都对内存访问做过优化,但是Synopsys音频子系统是通过优化架构来实现了更高的容忍度。

看到此解决方案能够支持具有24位精度的从2.0到7.1声道音频流,估计要开发出与3D显示相匹配的音频产品也会轻而易举了,美丽的画面加上美妙的声音才能堪称完美。

评论