一种多路可编程高速时钟电路的设计

摘要:本文采用博亚20MHz高稳定度晶体振荡器、集成VCO的低相位噪声锁相环时钟芯片LMX2531、高精度时钟扇出器HMC987LP5E和多阶低通滤波器,实现具有低相噪特性的4路并行输出、频率最高为2.5GHz的高速时钟电路的设计。文中给出了多路可编程高速时钟电路系统的原理框图,并详细论述了控制寄存器的参数配置以及初始化顺序过程。该时钟电路已应用于20GSa/s数字示波器的高速ADC采样模块中,实际测试及工程应用均表明,整体指标达到设计要求。

本文引用地址:http://www.amcfsurvey.com/article/134922.htm引言

近年来,我国电子与通信技术的飞速发展对时域信号测试和分析提出了更高的要求,在高速数据采集与波形处理方面尤为突出。高速数据采集的关键部分为模数转换器(ADC),影响ADC性能的因素有很多:输入模拟信号的频率大小及阻抗、取样时钟的抖动质量、供电电源的去耦情况、印制板的布局布线等。ADC的动态性能受取样时钟的相位抖动(Phase Jitter)影响很大。许多现代高速、高性能ADC都要求低相位噪声(低抖动)的时钟,以保证其能工作到GHz频率范围。目前市场上可购买的ADC芯片难以满足单片20GSa/s取样率的要求,本设计中采用4片5GSa/s的EV10AQ190[3]交叉采样来实现。

每路ADC都单独需要一路2.5GHz高速、高稳采样时钟,传统的晶体振荡器虽然能提供低抖动时钟信号,但是不能工作到GHz以上频率。为了保证4路ADC在各自2.5GHz取样时钟下有着较高的等效分辨率和输出信噪比,本文在时钟电路设计上采用高稳定度晶体振荡器、集成VCO的低相位噪声锁相环时钟芯片LMX2531、高精度时钟扇出器HMC987LP5E和多阶低通滤波器来实现高频率低抖动的设计要求。文章最后给出工程应用的测试和分析结果。

时钟抖动的影响及分析

时钟抖动对ADC信噪比及转换精度的影响

a. 采集时钟抖动对ADC信噪比的影响:

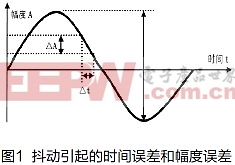

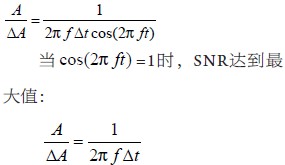

取样时钟的抖动能够导致ADC取样与触发时间关系上的错误,如图1所示。取样时间△t的不确定性,导致幅度的不确定性,即在输入信号幅度上造成错误的取样,因此降低了ADC的信噪比(SNR)。根据图1表达的取样时间的不确定性,可以得到信噪比模型。对于给定的时钟抖动量,数据转换器的SNR能够用如下公式计算。

模数转换器相关文章:模数转换器工作原理

低通滤波器相关文章:低通滤波器原理

锁相环相关文章:锁相环原理

评论