基于FPGA的NoC验证平台的构建

研究人员从拓扑结构、路由算法、交换策略以及流控机制等多个方面对NoC进行研究,但是如何构建NoC验证平台,快速得到NoC的性能也一直是NoC研究的重点。

在过去的几年里,一些研究机构提出了对于NoC不同抽象层次的验证方法的研究,一般的NoC验证是基于软件的仿真和建模,如:用C、C++、SvstemC进行系统级建模仿真,这样验证很灵活,但在仿真时间上却开销很大。本文提出的基于FPGA的NoC验证平台在仿真速度方面是一般基于HDL的软件仿真的16 000倍,而基于PC机编写的NoC软件更增强了该平台的灵活性和实用性。

1 验证平台架构

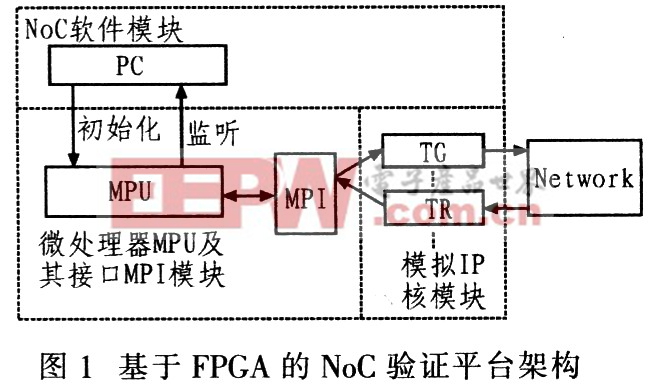

该验证平台采用模块化设计,可以很容易地对不同的NoC进行功能验证和性能评估。图1给出了该验证平台的基本架构。

它主要包括3个模块:

1)模拟IP核模块 该模块包含有数据流量产生器TG(Traffic Generator)模块及数据流量接收器TR(Traffic Receiver)模块。TG模拟产生NoC网络中各个IP节点可能产生的数据流量,TR用于收集NoC运行过程中的各种信息。TG/R作为一个IP节点和待测NoC中的每个交换节点相连接。

2)微处理器MPU及其接口MPI模块 PC机通过MPU(FPGA中自带的NiosⅡ软核)和MPI实现对NoC各IP核中TG内部各个配置寄存器的配置,并将TR中各个寄存器的内容读取到PC机中进行处理。本模块和模拟IP核模块构成FPGA硬件平台。

3)NoC软件模块 完成对NoC的配置以及NoC系统的性能统计。PC机通过MPU与FPGA进行通信,实现对NoC的配置并从FPGA中得到数据并进行后端处理,以图形的方式显示给用户,供用户对所设计的NoC进行评估。同时PC机可以监控NoC运行的情况。

FPGA采用Ahera公司Stratix IV系列中的EP4SGX230KF40C2,该器件能够提供高速的时钟信号和大量的片内资源,并具有大量外围接口电路可供使用,这为基于FPGA的验证提供了强有力的保证。

1.1 流量产生器TG

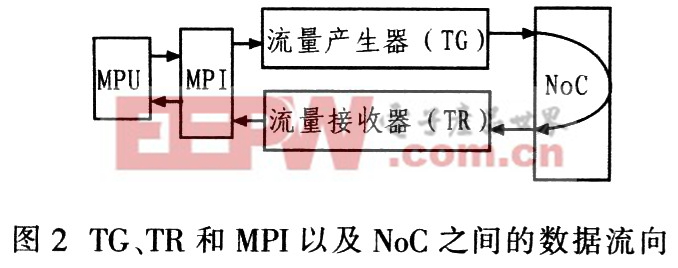

该平台中的TG是一个可重用的软核,用户可以通过为配置寄存器写入不同的配置信息使其产生不同的流量并注入NoC中。TR用于接收数据信息,并统计发包数和收包数。

记录延时信息,统计误码个数。图2给出了TG、TR和MPI以及NoC之间的数据流向。

在片上网络中,流量的分布由以下2方面决定:1)流量的源/目的节点对的分布,即空间位置上的通信概率分布,称为空间分布;2)流量注入网络时,注入网络的时间间隔在时间上呈现的概率分布,称为时间分布。为了使该平台达到评价NoC性能的目的,流量产生器TG将从空间分布和时间分布的不同,模拟出不同的流量。

空间分布主要包括:1)给定目标地址:即配置TG产生发往确定目标地址的数据包;2)均匀分布:即配置TG产生均匀的发往网络中各个节点的数据包,类似于网络中的广播现象;3)热点分布:即配置TG产生发往网络中一些特定的数据交换相对频繁的节点的数据包;4)局部分布:即配置TG产生发往网络中某一局部的网络距离较近的节点的数据包;5)矩阵转换地址分布:即按照矩阵X,Y向量转置的特点。配置TG产生发往与发送节点地址相对应的节点的数据包。

时间分布主要包括:1)确定时间间隔:即配置TG每过一定数目的时钟周期发送1个数据包,直到停止发包为止;2)自相似流量模型:即ON-OFF流量模型。即配置TG在一段时间内发送数据包,在一段时间内停止发包。此类流量模型就是模拟现实中在某一段时间突发很大的流量,而在另外的时间段不产生流量;3)随机分布:即配置TG在发送1个数据包之间的间隔是1个随机时钟周期数。

空间分布和时间分布一般会交错配置使用,那么组合之后可以产生十几种不同的流量模型。另外,数据包的格式可以是用户指定的数据,也可以是伪随机序列PRBS(Pseudo Random Binary Sequences)。数据包的大小亦可由用户指定,以数据片为单位,最小的数据包包含4片,最大的数据包包含511片。那么将流量模型和数据格式以及数据包的大小组合起来,就会产生种类更为丰富的流量模型。

流量产生器TG内部设有多个配置寄存器,包括:发包使能寄存器,发包间隔寄存器,发包地址和数据寄存器以及发包类型寄存器。这些寄存器统一编址,用户可以通过配置这些寄存器控制TG工作。

1.2 流量接收器TR

流量接收器TR用于收集收发包数目,收发包的收据片,并且统计误码和时延信息。为了达到此目的,TR内部设有多个只读寄存器,包括:发包个数寄存器.收包个数寄存器,发包数据寄存器,收包数据寄存器,中断寄存器,误码计数器以及延时寄存器,延时寄存器可以保存最近80个包的延时信息。这些寄存器统一编址,可以通过访问这些寄存器来读取各种用于功能验证和性能评估的原始数据。

1.3 微处理器MPU及微处理器接口MPI

微处理器MPU是在QuartusⅡ软件的SOPC Builder工具中定制的。它包括1个NiosⅡ处理器IP核和外围的一些并行输入输出接口。NiosIⅡ系列嵌入式处理器是一款通用的RISC结构的CPU,使用32位指令集结构(ISA)的二进制代码兼容。将NiosⅡ处理器嵌入到FPGA硬件平台中,配合整个系统实现验证的功能。该平台在所定制的NiosⅡ处理器的外围还加入读信号、写信号、地址信号、输入数据信号、输出数据信号和中断信号等,来完成PC机和FPGA硬件平台之间的数据通信。

NiosⅡ处理器外围还包括一个锁相环(PLL)软核,用于提供NoC电路中所需要的各种时钟频率。微处理器MPU与TG/R通信时,读写控制时钟作为突发时钟,频率一般比较低。而NoC中交换节点之间的数据交换会由于特定电路的不同,工作时钟频率会大小不同,那么根据此工作频率,PLL产生相应的时钟信号配合其工作。MPU处理器仅占Stratix IVEP4SGX230KF40C2器件2 820个逻辑资源LE (Logic Element)(即1%)。因此使用非常高效。

该平台还提供一个通用的微处理器接口MPI,用于保障MPU和TG/R之间的数据通信,也为MPU和TG/R的重复使用提供了统一接口。

1.4 NoC软件

NoC软件主要完成对FPGA硬件平台的初始化配置和信息收集及统计处理。根据功能划分为2部分:

1)NoC测试部分 其基本功能包括对FPGA硬件平台的各个IP中TG内部配置寄存器的初始化配置,启动产生数据流并注入到NoC中,同时对NoC的运行情况进行监控,并实时收集与功能验证和性能评估相关的信息。该软件是在NiosⅡ的集成开发环境(IDE)下用C语言设计开发的,在GNU的编译器下编译之后形成可以下载到MPU上直接运行的二进制文件。

2)NoC性能统计处理部分 该部分的主要功能是借助于第三方绘图工具按照NoC性能统计规则对收集到的数据进行统计处理,并以图表的方式直观显示NoC的基本功能和统计学性能。

以上两部分都是在PC机上开发完成的,可应用于对不同NoC的测试与验证。这为基于FPGA的硬件验证平台增强了灵活性和实用性。

2 仿真验证流程

该验证平台的验证流程包括FPGA硬件平台的构建和对该硬件平台的初始化配置以及NoC运行之后的信息收集和统计处理。仿真验证流程如图3所示。

评论