超宽带系统中ADC 前端匹配网络设计

1. 引言

本文引用地址:http://www.amcfsurvey.com/article/153559.htm传统的窄带无线接收机,DVGA+抗混叠滤波器+ADC 链路的设计中,我们默认ADC 为高阻态,在仿真抗混叠滤波器的时候忽略ADC 内阻带来的影响。但随着无线技术的日新月异,所需支持的信号带宽越来越宽,相应的信号频率也越来越高,在这样的情况下ADC 随频率变化的内阻将无法被忽视。为了取得较好的信号带内平坦度,引入了ADC 前端匹配电路的设计,特别是对于non-input buffer的ADC在高负载抗混叠滤波器应用场景下,前端匹配电路的设计在超宽带的应用中就更显得尤为重要。本文将以ADS58H40为例介绍ADC前端匹配电路的设计。

2. Non-input buffer ADC 内阻特性及其等效模型

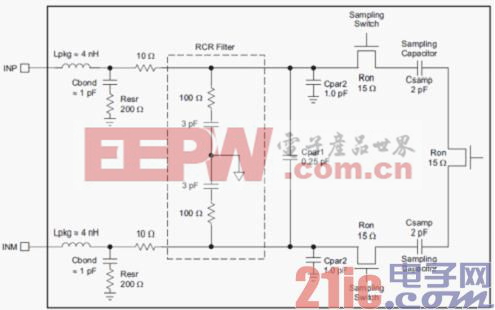

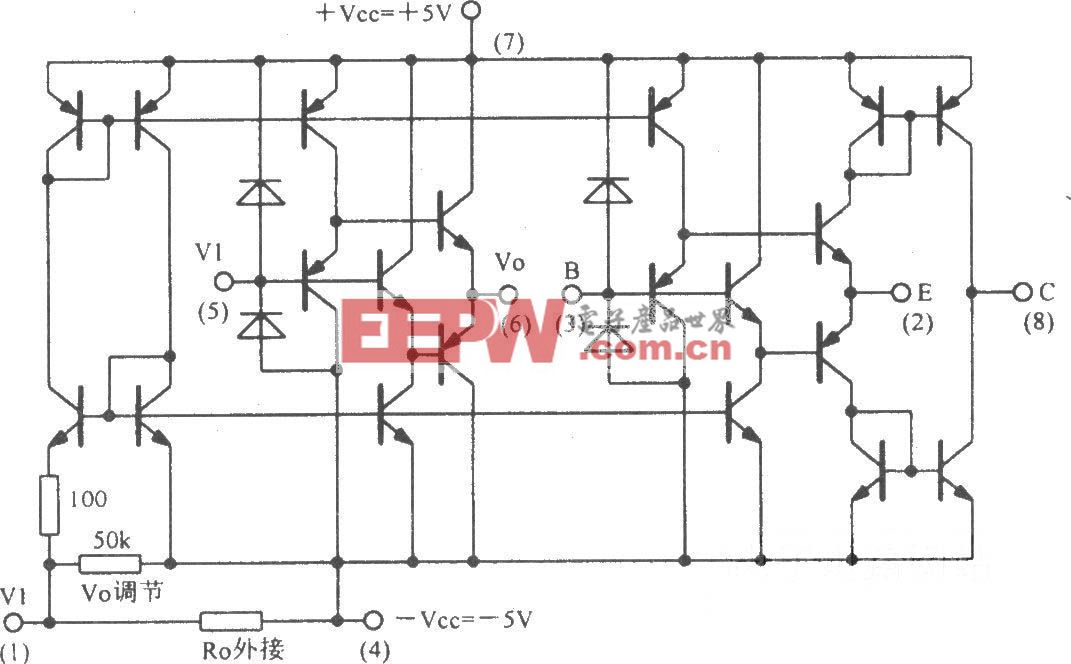

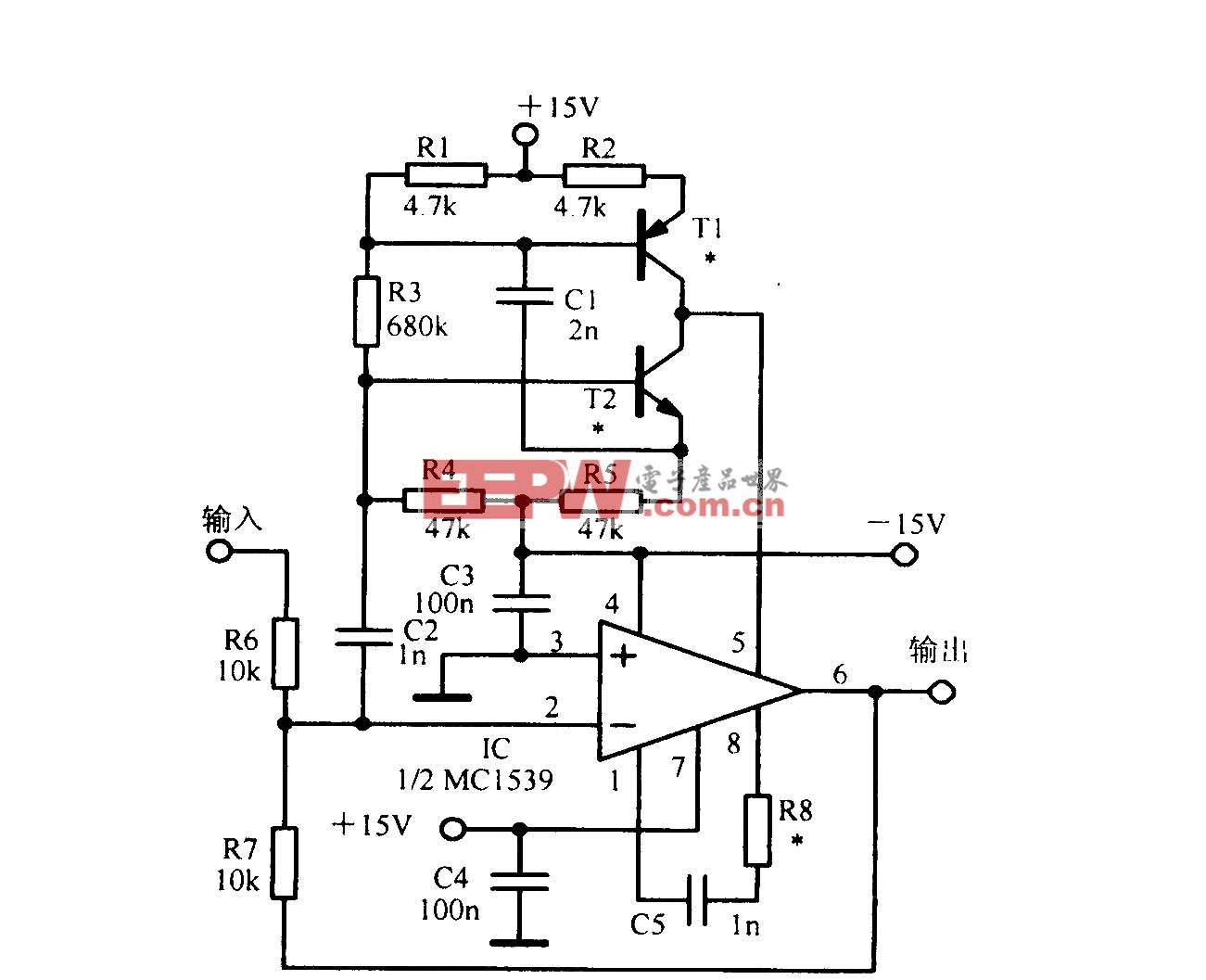

理想ADC 的输入内阻应该是高阻态,即在前端抗混叠滤波器的设计中无需考虑ADC 内阻带来的影响,但是实际ADC内阻并非无穷大并且会随着频率而发生改变。从输入内阻的角度而言,ADC又可以被分为两类,一个是有输入buffer的ADC,输入特性更趋向于理想ADC,内阻往往比较大;另一类就是没有输入buffer的ADC,它们的内阻在高频不可忽略且随频率发生改变,但它们的功耗比前者要小。图1为non-input buffer ADS58H40模拟输入等效内阻模型。ADC模拟输入端采样保持电路本身所等效的阻抗网络随频率的改变而变化;再加上ADC 采样噪声的吸收电路(glitch absorbing circuit)RCR 电路,它的存在改善了ADC 的SNR 和SFDR,但也使得ADC的内阻随着频率而越发变化。两者效应叠加使ADC 的等效负载整体呈现容性。

图1 ADS58H40 模拟输入等效内阻模型

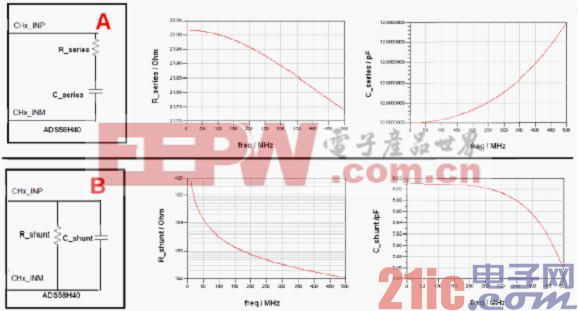

图2以ADS58H40为例给出了内阻随频率变化的曲线图。A串联模型,串联模型中的串联等效电阻值在Ohm量级。B并联模型,并联模型中的并联等效电阻值在低频( 100MHz)的时候kOhm量级,但随着输入频率不断升高(>200MHz),并联等效电阻值会急剧下降到百欧姆级,使其相对于抗混叠滤波器ADC端负载不可忽略。而且不管是并联模型还是串联模型中的等效电容,也使得抗混叠滤波器ADC端负载特性偏离理想的阻性特征需要补偿。

图2 ADS58H40 内阻简化模型:A 串联模型,B 并联模型;及其相关频率变化曲

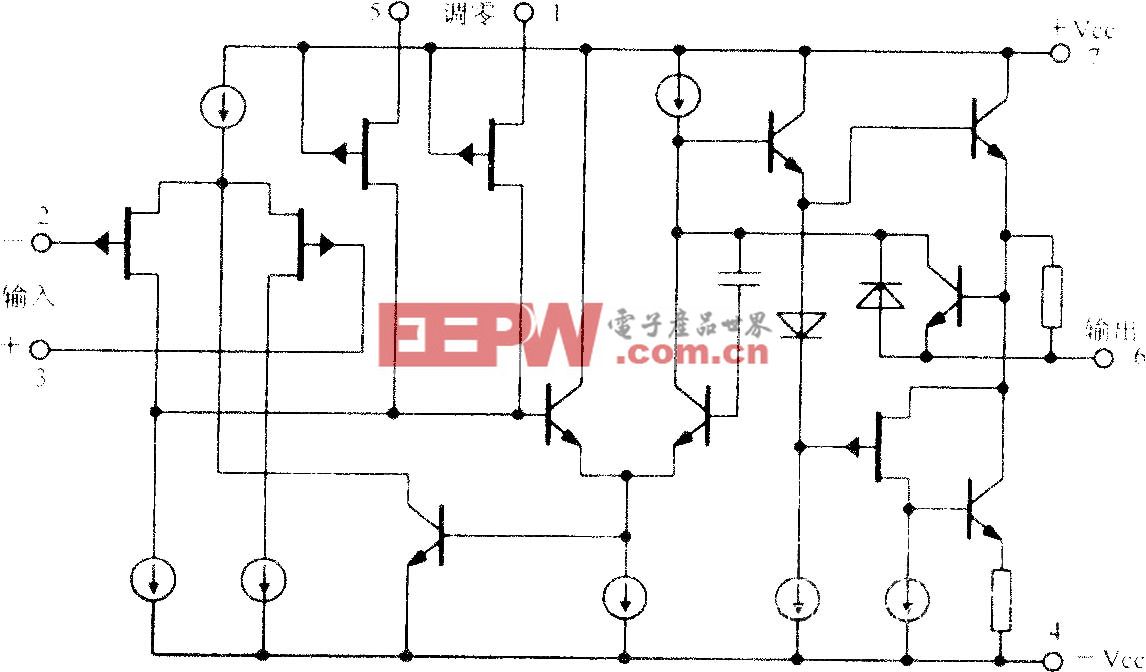

3. Non-input buffer ADC 前端匹配网络拓扑架构

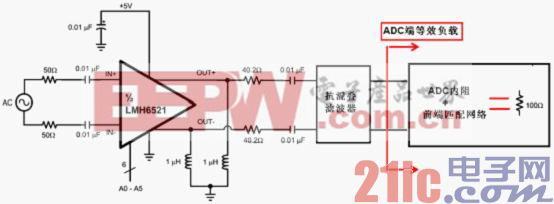

由于ADC 的等效内阻随频率变化而且在高频时偏离理想高阻态,抗混叠滤波器ADC端负载阻抗的选择就显得尤为重要。理想ADC支持抗混叠滤波器的负载的任意选择,完全没有要求。但是内阻的变化,使得现实中ADC希望前端的抗混叠滤波器的负载阻抗可以比较小,即传统50Ohm 抗混叠滤波器的设计,ADC的kOhm级的内阻相对于50Ohm而言可以忽略不计。但是现在越来越多的抗混叠滤波器需要100Ohm 的负载设计,以达到前端驱动级的最优工作状态。图5 以现在无线基站设计中常用的DVGA LMH6521 为例,为了使整个接收链路达到最优的线性性能,推荐使用100Ohm 的抗混叠滤波器。此时如果仍采用简单的100Ohm 负载并联在ADC 输入端的做法,随着输入信号频率的升高和输入信号带宽的增宽,ADC内阻非理想特性将越来越明显,它会直接拉低ADC 侧的100Ohm 负载,恶化信号的带内平坦度。

图3 DVGA 最优工作状态负载要求示意图

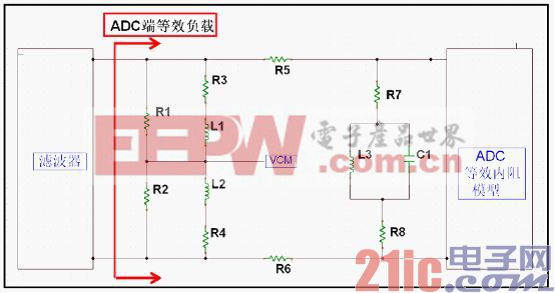

为了统一抗混叠滤波器的设计以简化其在不同平台项目中的移植,希望ADC侧(包括ADC 等效内阻和前端匹配电路)在整个信号带宽中都呈现一致的阻抗特性例如图3 应用中的100Ohm, 引入了ADC 前端匹配网络如图4 所示。

图4 Non-input buffer ADC 前端匹配网络拓扑架构简图

其中,

1) R1和R2是ADC侧阻抗的主要组成部分,在假设ADC理想高阻特性的情况下,它即代表了ADC侧的负载。由于ADC有限内阻和所需的匹配网络,为了达到整体效果仍保持100Ohm负载状态,R1和R2远高于50Ohm的最优取值。R1和R2不仅决定了ADC输入pin脚的实际共模电压(VCM-Analog input common mode current*R1, ADC的性能SNR 和SFDR会随着VCM的变化而发生些许改变,请参见datasheet图22);而且原本也是sampling glitch的低阻泄放路径,所以不宜过大。R1和R2的取值原则为实现ADC端组合负载目标前提下的最小值,而且最大值不宜超过100Ohm。

2) R5和R6代表ADC输入口串联的5Ohm或者10Ohm的阻尼电阻,为的是衰减可能由bonding wire寄生电感引起的震荡。

3) 由R3-L1-L2-R4组成的网络主要是负责超宽带应用中的带内平坦度调整,它存在的意义在于此网络呈感性,阻抗随频率递增;它和随频率递减的ADC 等效内阻呈反方向变化,两项并联使整体阻抗在所需频率范围内尽量保持不变。如果觉得网络过于复杂,也可以考虑将L1 和L2 合并为一个电感断开VCM 连接;考虑分隔为两个电感仅是为VCM电流提供和R1+R2 并行的通路以减小VCM距理想值的偏移。

4) R7-L3//C1-R8组成的网络则主要担负吸收sampling glitch的责任。在50Ohm负载抗混叠滤波器的应用中,50Ohm负载路径即相当于采样噪声的低阻泄放路径,所以R-L//C-R电路选配一般可以不加,但是当抗混叠滤波器的负载阻抗增加,例如上文中所提到的100Ohm抗混叠滤波器的应用,R-L//C-R的网络在性能要求较高的应用中建议采用。采样噪声是由采样开关的开关切换引起的。只有在ADC输入pin脚处直接引入低阻通路才可以有效的将其吸收,这就是为何RLCR 网络需要尽可能的接近ADC输入管脚布局。否则,采样噪声会在dither的作用下转化为影响ADC性能的噪声从而恶化SNR和SFDR。此吸收采样噪声电路的最主要的组成部分为电容,采样噪声多为高频分量组成,对其形成低阻通路即低通电路或带通电路(对有用信号为高阻,对高频噪声为低阻)。C的取值不易过小,过小影响吸收效果,同样也不易过大,过大会严重影响输入带宽。两端串联的R不易过大25Ohm为宜,并联的电感主要是降低Q值,有助于平坦带内波动。当R3-L1-L2-R4 和R7-L3//C1-R8网络共存的时候,出于带内平坦度的考量,需要移去L3形成R-CR网络。

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

评论