迎合3.5G/4G基站Serial RapidIO架构趋势的解决方案

随着用户对于行动数据需求的增加,电信服务业者必须快速地布建 3.5G 和 4G 基站。这也使得下一代基站的架构需要高频宽的背板,以容纳多重的基频卡(baseband card)数据传输的需求,而基频板则需要数组的多核心数字信号处理器(DSP),以提供更强大的基频处理能力。富威集团代理的IDT方案是如何满足这些要求的呢?

本文引用地址:http://www.amcfsurvey.com/article/157620.htm随着用户对于行动数据需求的增加,电信服务业者必须快速地布建 3.5G 和 4G 基站。这也使得下一代基站的架构需要高频宽的背板,以容纳多重的基频卡(baseband card)数据传输的需求,而基频板则需要数组的多核心数字信号处理器(DSP),以提供更强大的基频处理能力。为配合 DSP 效能的提升,必须以高频宽连结去执行与多重 DSP 的互连,同时要降低布线次数(trace count),让基板设计更为容易。不断成长的 IDT Central Packet Switches(CPS)系列可支持 Serial RapidIO(sRIO),提供最广泛的端口和连结数组组合,使模块化基站架构可以轻易扩充。

使用者需求促使无线基础建设提升

在过去几年间,无论是在固定和行动网络市场中,网络流量都呈现惊人及快速的成长。对行动网络而言,最近对于3G智能型行动电话,以及PDA类型装置需求的增加,将继续驱动企业市场端的行动数据流量不断增加。就一般消费角度来看,在可预见的未来内,造成数据流量不断增加的最大因素,将是影像收看和分享的下载需求。用户希望能有更快的网络速度和更短的下载时间,同时又追求丰富的媒体经验,这都将鼓励电信服务业者在他们既有的无线设备组合上,增加具有更强大能力的3.5G和4G基站。

在3.5G和4G基站架构中,数据传输速率能力的增加,以及对于每一基站更高用户容量的追求,都促使射频和基频卡之间的背板速度提升。因此,整体频宽的增加,便逐渐造成基频卡上的标准组态,拥有更多的多核心DSP互连。

富威集团所代理的IDT以Serial RapidIO(sRIO)迎合下一代基站的需求

当为了减少互连布线,以维持板子的大小,来符合系统频宽的增加,sRIO渐渐成为基频卡架构的标准协议。做为一种开放式标准,sRIO结合了可达到高频宽高效率的封包,以及直接的点对点支持,对于要在基频应用中支持多重DSP而言,这样的结合是很理想的。

数据封包要在DSP、处理器、FPGA、其它交换组件,或是任何其它sRIO基础的装置间快速及正确地依循路径进行传输,中央封包交换Central Packet Switch(CPS)扮演着关键性的角色。 sRIO 启动的 DSP、 特定应用信号处理器(ASSP)和可程序化逻辑门阵列(FPGA)供应的不断增加,已相当于一个健全的生态系统,可为下一代基站提供高效能、 具成本效益、模块化的解决方案。

对于电信服务业者而言,要以具成本效益的方式,为特定的无线基础建设布建正确数量的系统频宽能力,以符合成长中的使用者频宽需求,无疑是一项巨大的挑战。最成功的基站业者将为电信服务业者提供一种易于扩充 、模块化、具有共通平台的基站架构,以推动 WCDMA、LTE、WiMAX ,和 CDMA2000 间的跨技术再利用。

针对基站架构的扩充性、可组合性和可再利用性,具有弹性的sRIO互连解决方案,可满足这种种的要求:包括基频卡上各种不同 DSP 的互连,以及多重基频卡间的互连。一个典型的基频架构拥有一个单一的 sRIO 交换器,以做为多重 DSP 和其它组件间的链路汇集点,例如控制处理器,也有可能是 FPGA。如果是多重基频卡,它们则可能会连接至另一个交换器,可能也是 sRIO。目前的 sRIO 1.3 版本在 1.25G、 2.5G 和 3.125G 信道速度中,支持每端口1x和4x通道组态。对于任何特定的基站架构,根据系统频宽和用户容量目标,不同信道速度的1x和4x信道端口组合非常多元。在1.25G、 2.5G 和 3.125G 信道速度中常用的1x至4x通道,最终应会移转至由 sRIO 2.0 版本所支持的每一通道 5G 和 6.25G。

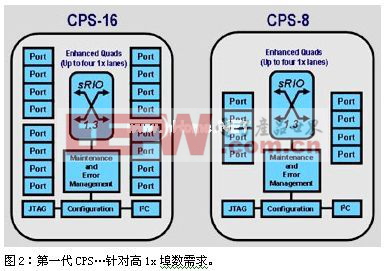

第一代 CPS-16 和 CPS18 装置已针对板子等级的 DSP 群组应用进行最佳化。它们的主要功能为具有一背板接口,如此可连至背板交换器,或是直接连至多重 RF 卡。

评论