FPGA攻略之Testbench篇

Testbench,就是测试平台的意思,具体概念就多不介绍了,相信略懂FPGA的人都知道,编写Testbench的主要目的是为了对使用硬件描述语言(HDL)设计的电路进行仿真验证,测试设计电路的功能、部分性能是否与预期的目标相符。初学者往往把写RTL代码当成重点,不愿写Testbench,包括小朱同学也是,仅仅使用Quartus II自带的仿真产生几个激励,然后观察一下最后输出的波形就完事了,甚至某些时候直接忽视仿真,拿单片机在线调试那一套来对付FPGA,直接把代码下载到板子里看效果,若与预期不符,再修改代码,再次下载到板子,如此反复,直到某一天实在玩不下去了。

本文引用地址:http://www.amcfsurvey.com/article/184677.htm同志们,FPGA真不带这么玩的!赶紧禁止自己使用Quartus II自带的仿真,甭画波形图了,你画成大师也没用(也成不了大师,Quartus II只能做极初级的仿真)!如果你立志从事FPGA行业,那么会写Testbench才你的敲门砖,而且别想着去公司写RTL代码了,向毛主席保证,公司一定是让你来写Testbench的。再赶紧把你的FPGA开发板有多远扔多远(别丢,还是要用的),FPGA不是单片机,学习FPGA并不那么需要开发板。打个比方,学习FPGA是两万五千里长征,那么使用开发板连三千里都占不到,远远不到。对于FPGA,仿真验证才是核心,这么讲吧,验证占到整个设计工作的70%,前仿真、后仿真、功能仿真、时序仿真、行为级仿真、RTL级仿真、综合后仿真、门级仿真、布局布线后仿真……好吧,别晕,本篇只讲Testbench,Modelsim仿真咱们下篇再讨论。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。借用一下特权同学总结的编写Testbench的三个基本步骤:

1、对被测试设计的顶层接口进行例化;

2、给被测试设计的输入接口添加激励;

3、判断被测试设计的输出相应是否满足设计要求。

逐步解决编写Testbench的这三点:

首先“对被测试设计的顶层接口进行例化”,这一步相对比较简单,例化就是,但端口多时也够喝一壶的,而且要分wire、reg,有时会弄错,别难过,其实可以偷个懒,通过Quartus II自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulationModelsim文件夹下的.vt格式文件。这一步就不多讲了,偷懒就挺好。

其次“给被测试设计的输入接口添加激励”,一般时序设计必然涉及到最基本的两个信号——clk、rst_n(时钟、复位),肯定有童鞋会讲可以没有rst_n,是可以没有,但何必呢,让代码更健壮一点不很好嘛,别钻牛角尖。下面攻克clk、rst_n的写法:

首先先讲一下timescale,因为想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。 `timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

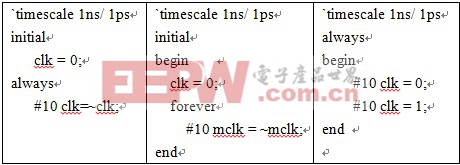

clk大体上有三种写法 :

上述三种代码的目的就是产生系统时钟,给clk一个初值后,不断重复执行:每10ns翻转一次clk,从而生成一个周期为20ns,频率50MHz的方波信号。第一、二种基本类似,第三种比较简单,少了一个initial,放在了always里初始化。

三种方法都无一例外地给clk赋了初值,因为信号的缺省值为Z,如果不赋初值,则反相后还是Z,时钟就一直处于高阻Z状态。小朱同学一般选中第一种,看个人喜欢。

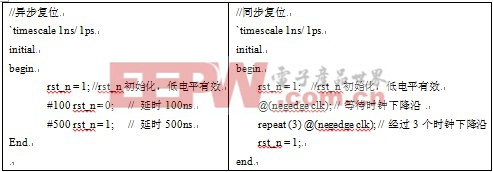

根据复位方式的不同,rst_n一般有两种写法:

fpga相关文章:fpga是什么

评论