DS2409 MicroLAN耦合器替代方案设计

摘要:DS2409的设计初衷是将其用做门禁控制的探测点(即读取头)以及用来减少大型1-Wire®网络中总线上的负载。DS2409也被用来实现双主机网络。但目前Maxim已经决定停止生产DS2409并鼓励所有使用DS2409的客户实施相应的设计改进以应对这个情况。这篇应用笔记介绍了使用DS2409的1-Wire网络系统的替代方案,这些方案并不要求对现有的网络进行重新设计。

本文引用地址:http://www.amcfsurvey.com/article/185727.htm概述

得益于DS2409 MicroLAN耦合器的独特设计,它可以被用于实现多种特殊应用。本文首先列出了DS2409的特性和应用,接着介绍了可以实现相同功能的替代电路。最后本文对这些替代电路做了详细讨论。

DS2409特性描述

DS2409是一个特殊类型的2端口可寻址开关器件。与向传统的可编程输入/输出口(PIO)输出高、低电平不同,这个器件通过传输门来将其输出通道与作为其输入的1-Wire总线连接。在任何时刻,只有一个1-Wire输出通道有效。除了1-Wire输出通道以外,DS2409还有一个可控输出通道,该输出通道可以配合主输出通道使用(默认方式),也可配合辅助输出通道使用,还可以独立使用。这些功能的切换是通过控制状态控制字节来完成的(参见DS2409数据资料)。状态信息字节(参见DS2409数据资料)允许主机确认设备配置状况、检查器件工作状态(使用或非使用状态)、确认每个1-Wire输出的逻辑状态(高或者低)、事件标志位(置位/清零)。表1总结了DS2409的这些特性以及这些特性带来的便利。

表1. DS2409特性及优势

DS2409需要5V VDD供电,上电后,所有1-Wire输出通道都处于非工作状态,并通过内部上拉电阻拉到5V VDD电平。短暂的电源掉电将使器件进入上电复位状态。在VDD稳定后,1-Wire输入端口作用一个短暂低电平,使DS2409进入软件上电复位状态。当DS2409重新和主机连接后,器件进入默认的上电复位配置状态,1-Wire总线输出通道都处于非工作状态,事件标志位状态不确定。

表1列出的特性主要面向下列3种应用:智能探测点、多层网络、双主机网络(参见表2)。

表2. 特性及其应用

智能探测点

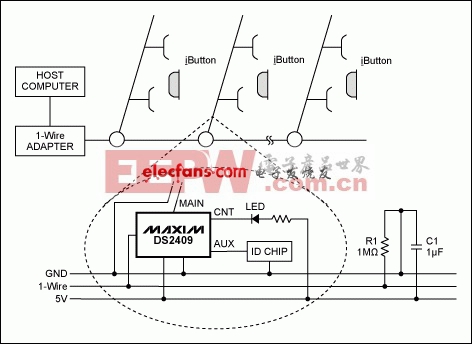

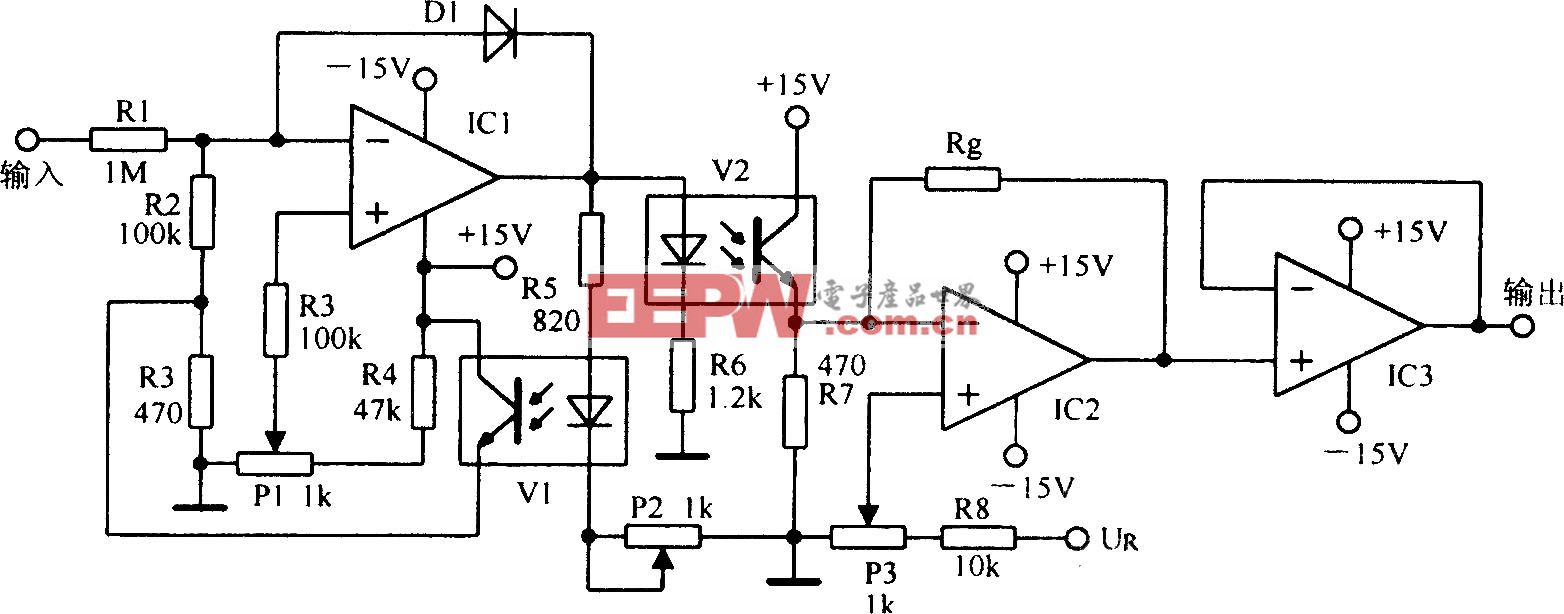

图1所示框图是将iButton®作为电子钥匙的门禁系统。R1/C1应尽量靠近1-Wire适配器安装。R1的作用在于当1-Wire总线中断时,DS2409可以实现一个软复位。C1在VDD过冲时可以避免DS2409阻塞1-Wire总线。

图1. 带智能探测点的门禁控制系统拓扑

除了主1-Wire总线外,探测点(如DS9092 iButton探头)位于DS2409主输出端分支二级网络上。与辅助输出口相连接的是一个ID芯片,比如一个1-Wire EEPROM器件,这个器件中存储了分支名称。正常工作情况下,所有分支都处于禁止状态(即与主1-Wire总线断开),与此同时主机在进行条件搜索,检测事件是否发生。当一个iButton连接到探测点时,将该分支上的DS2409事件标志位置位。在下一个扫描周期中,主机将定位于该DS2409并使能辅助输出通道,以读取分支名称。接下来,主机将访问相同的DS2409并且使能主输出通道,以访问接入系统的iButton。当主输出通道进入工作状态后,点亮LED,指示用户已检测到器件连接。如果不需要点亮LED,控制输出可以连接到一个门锁,软件控制打开/关闭。由于Smart-On命令具有短路检测功能,DS2409可以防止探测点短路所引起的网络故障。

多层网络

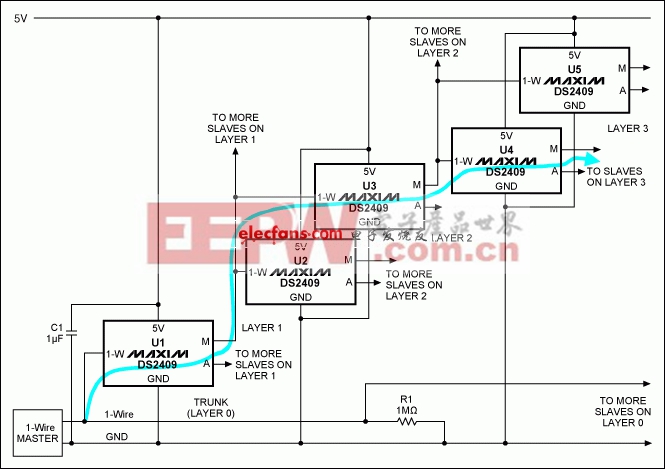

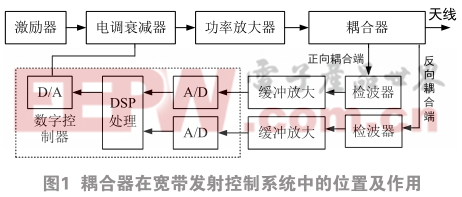

对于任何网络,找到主机驱动负载和节点(或分支、从机)数量间的最佳平衡非常重要。达到这个目的一种方式是网路分层(参见图2)。图中展示了一个4层网络,从始终保持有效状态的主干开始(第0层),每个子层都包含开关分支(第1层到第3层)。R1/C1应靠近1-Wire主机。如果通过1个或多个DS2409在1-Wire主干层和子层构建多层网络,R1将保证主机再度连接时自动关断通路。C1在VDD过冲时避免DS2409阻塞1-Wire总线。

为了有效控制这种网络,主机应当了解每层各个分支DS2409从机的ROM ID,以识别网络拓扑。为了打开第3层从机的通路(如箭头所示),主机应执行下列命令:

对主干U1执行Match ROM命令。

使能主输出通道(该操作将打开第1层两个从器件的通路)。

对第1层U3执行Match ROM命令。

使能主输出通道(该操作将打开第2层的两个从器件通路)。

对第2层U4执行Match ROM命令。

打开辅助输出通道(该操作将打开第3层连接至该输出的从器件通路)。

图2. 多层网络拓扑

由于采用VCC供电,DS2409的最大1-Wire总线负载是100pF (50pF来自1-Wire总线输入,50pF来自输出),而典型的寄生供电1-Wire器件总线负载为800pF至1000pF。在示例拓扑中,主机所要驱动的总负载是:主干网上的DS2409 (50pF)、第1层的两个DS2409 (150pF,2个输入、1个输出)、第2层的两个DS2409 (150pF),连接在U4辅助输出通道的所有从器件(50pF加上从机负载)。因此总负载是400pF加上从机负载。

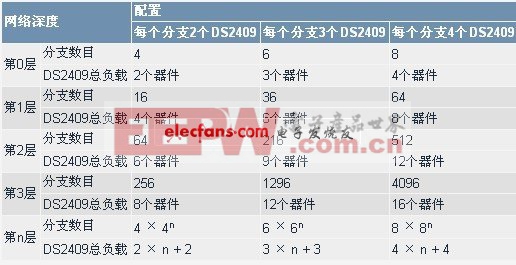

根据应用需求,在每个分支可以挂接多于2个DS2409,表3列出了最大分支数目以及相应的来自于耦合器的负载。层与层之间,分支数目呈指数方式增长,然而来自DS2409的负载则呈线性增长。

表3. 多层分支数与DS2409负载

除了随网络层数增加而线性增加的通信负荷外,用户同时应注意DS2409所引入的阻抗。对于主输出来说,典型值是10Ω (最大值20Ω);对于辅助通道来说,典型值是15Ω (最大值30Ω)。非零阻抗降低了最终网络层(主机至从机)的高电平,并拉高了主干网(从机至主机)的低电平。降低高电平通常不是什么问题,但是由于低电平阀值被拉高,通常建议用户将网络分层控制在4层或4层以内。

评论