ADC设计挑战:从高性能转向低功耗

新的应用需求不断推动模拟技术的发展:性能越来越高,集成度不断提高。ADC产品作为模拟IC的重要成员,在符合上述发展的趋势下,还存在自身的特点……

当使用“巧克力”手机时,不用按键只用轻触那泛着深红色光的区域,你是否知道电容感应技术改变了你的体验;当看到那小小的骑车机器人“村田顽童”可以前进、倒退、爬坡并且停而不倒时,你是否知道其中使用了多种传感器以检测各个方向的倾斜角度和探测道路状况;当你惊叹残疾人可以自如地控制假肢完成复杂动作时,你是否知道与假肢相连的探测器可以检测人体肌肉的最细微运动从而实现对假肢的控制;也许你并没有留意到用手机通话时显示屏会自动关闭以便降低功耗,这是手机检测到显示屏被物体(例如耳朵)遮住时的操作……所有这些都表明:用户体验推动半导体和技术创新的进步,并在同时对模拟IC的性能提出更高要求。

同时,电子器件的集成度越来越高,例如AD9271在单一芯片上集成了一个完整的8通道超声接收器,其中的一个通道就包含低噪声放大器(LNA)、可变增益放大器(VGA)、抗混叠滤波器(AAF)和12位 ADC。虽然集成是大趋势,但是还需要考虑成本,客户需要,技术要求,工艺发展等诸多因素。ADI大中国区资深业务经理周文胜说,“当性能指标要求特别高时,采用集成的方案并不明智;市场上需要什么样的芯片,芯片供应商就应该为实现这个系统去做一些相应的设计,ADI的‘智能分割’概念就是强调哪些功能模块应该集成,哪些功能模块要分开放,最终使设计达到最符合客户的要求,也符合技术要求。把所有的芯片集成在一起,当工艺都一样时,整体BOM可以降低;但当各芯片工艺不一样时,如果硬要把它们集成在一起可能会造成整个BOM上升。”

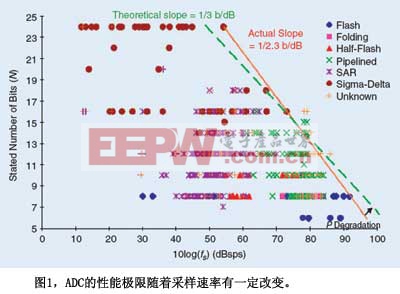

模数转换器(ADC)作为模拟IC的一种,也同样顺应上述模拟IC的发展趋势,但是它还遵循自身发展的规律。从最初的11位分辨率、50 kSps采样速率和500 W功耗的SAR型ADC到现在的16位分辨率、1MSps采样速率并且仅7 mW功耗的ADC AD7980, ADC的性能已经取得了巨大进步。现有ADC存在7种结构:falsh, half-flash, folding, SAR, pipelined, sigma-delta和未知结构。其中piplined和未知结构具有最佳的整体性能,所以它们非常适合例如无线收发器应用和军用等高性能要求的应用;SAR ADC具有最宽的采样速率,虽然它不是最快的,但由于低成本和低功耗使其很受欢迎。Sigma-delta ADC具有最高的分辨率,但是采样速度较低,从kSps到MSps;而flash ADC由于其并行结构具有最高采样速率可达GSps,但是由于非线性使其分辨率限制在8位以内。

在进行ADC性能比较时通常使用品质因数:P=2B×fs和F=(2B×fs)/Pdiss,其中B是SNR比特数,fs是采样速率;Pdiss是功耗。文献1认为,在开发高功率效率的ADC设计上取得了显著进步,但是,ADC的分辨率和速度的乘积P在1993年~1999年的6年中几乎没有进步。文献[2]针对4家主要IC制造商(ADI, Maxim, NS和TI)的ADC产品的3个通用性能指标(采样速率、分辨率和功耗)分析后认为:上述P并不是恒定的,而是在低采样速率下部分P有一些改善;在高采样速率下部分P有一定降低(见图1)。

Sigma-delta和flash转换器是上述7中结构中仅有的F随时间降低的两种结构。这两种ADC针对特定要求,只有较窄的应用范围,它们都需要牺牲更多的功耗用于实现更高性能,这导致了F的降低。余下的SAR, pipelined等5种结构满足速度和分辨率的中等应用要求,因而能获得更高的F。二十多年来,ADC技术的发展一直被新应用推动,从而促进P的增加。虽然UWB,OFDM和雷达系统等应用推动ADC性能极限发展,ADC设计的主要挑战已经从性能扩展转向降低功耗,这一挑战在移动通信和SDR应用中尤为突出。

评论